US009498635B2

# (12) United States Patent

# Dellamano et al.

#### (54) IMPLANTABLE HEAD LOCATED RADIOFREQUENCY COUPLED NEUROSTIMULATION SYSTEM FOR HEAD PAIN

- (71) Applicant: SYNTILLA MEDICAL LLC, Dallas, TX (US)

- (72) Inventors: **Harry Dellamano**, Santa Rosa Valley, CA (US);

(Continued)

- (73) Assignee: SYNTILLA MEDICAL LLC, Dallas, TX (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/989,674

- (22) Filed: Jan. 6, 2016

#### (65) Prior Publication Data

US 2016/0114174 A1 Apr. 28, 2016

#### **Related U.S. Application Data**

(63) Continuation-in-part of application No. 14/879,943, filed on Oct. 9, 2015, which is a continuation-in-part of

(Continued)

- (51) Int. Cl. *A61N 1/378* (2006.01) *A61N 1/36* (2006.01)

- (Continued)

- (58) Field of Classification Search CPC ...... A61N 1/3787; A61N 1/0504; A61N 1/36075; A61N 1/36125

See application file for complete search history.

# (10) Patent No.: US 9,498,635 B2

# (45) **Date of Patent:** Nov. 22, 2016

(56) **References Cited**

3 4

## U.S. PATENT DOCUMENTS

| ,727,616 A | 4/1973 Lenzkes |  |

|------------|----------------|--|

| ,612,934 A | 9/1986 Borkan  |  |

|            | (Continued)    |  |

#### FOREIGN PATENT DOCUMENTS

| CA | 2734775    | 2/2015  |

|----|------------|---------|

| EP | 0007157    | 1/1980  |

| WO | 2009158389 | 12/2009 |

#### OTHER PUBLICATIONS

PCT: International Search Report and Written Opinion of PCT/ US2014/51235; Feb. 19, 2015; 24 pages. (Continued)

Primary Examiner — Catherine Voorhees (74) Attorney, Agent, or Firm — Howison & Arnott, L.L.P.

#### (57) **ABSTRACT**

An implantable head-mounted, radiofrequency (RF) coupled, unibody peripheral neurostimulation system is provided for implantation in the head for the purpose of treating chronic head pain, including migraine. The system may include an implantable pulse generator (IPG) from which multiple stimulating leads may extend sufficient to allow for adequate stimulation over multiple regions of the head, preferably including the frontal, parietal and occipital regions. A lead may include an extended body, along which may be disposed a plurality of surface metal electrodes (SME), which may be subdivided into a plurality of electrode arrays. A plurality of internal metal wires may run a portion of its length and connect the IPG's internal circuit to the SME. The IPG may include an RF receiver coil and an application specific integrated circuit. The IPG may be capable of functional connection to an external RF unit for purposes that may include power, diagnostics, and programming.

#### 17 Claims, 37 Drawing Sheets

Inventors: Kenneth Lyle Reed, Dallas, TX (US); Robert Raymond Bulger, Dallas, TX (US); Claire Denault, Dallas, TX (US); Michael Steven Colvin, Newbury Park, CA (US); Paul Griffith, Santa Rosa Valley, CA (US); Francis Menezes, Simi Valley, CA (US)

#### **Related U.S. Application Data**

application No. 14/717,912, filed on May 20, 2015, which is a continuation of application No. 14/460, 139, filed on Aug. 14, 2014, now Pat. No. 9,042,991.

- (60) Provisional application No. 61/891,795, filed on Oct. 16, 2013.

- (51) **Int. Cl.**

| A61N 1/05  | (2006.01) |

|------------|-----------|

| A61N 1/372 | (2006.01) |

(52) U.S. Cl. CPC ...... A61N 1/36075 (2013.01); A61N 1/36125 (2013.01); A61N 1/37229 (2013.01); A61N 1/37247 (2013.01)

# (56) **References Cited**

#### U.S. PATENT DOCUMENTS

|               | 10/1000 | D 1                   |

|---------------|---------|-----------------------|

| 4,793,353 A   | 12/1988 | Borkan                |

| 4,819,647 A   | 4/1989  | Byers                 |

| 5,000,194 A   | 3/1991  | Van Den Honert et al. |

| 5,037,497 A   | 8/1991  | Stypulkowski          |

| 5,215,086 A   | 6/1993  | Terry, Jr. et al.     |

| 5,279,292 A   | 1/1994  | Baumann et al.        |

| 5,545,219 A   | 8/1996  | Kuzma                 |

| 5,733,313 A   | 3/1998  | Barreras, Sr.         |

| 5,876,425 A * | 3/1999  | Gord A61N 1/36032     |

| 5,670,425 A   | 5/1///  | 607/33                |

| 6016440 4     | 1/2000  |                       |

| 6,016,449 A   | 1/2000  | Fischell et al.       |

| 6,178,353 B1  | 1/2001  | Griffith et al.       |

| 6,236,892 B1  | 5/2001  | Feler                 |

| 6,246,911 B1  | 6/2001  | Seligman              |

| 6,516,227 B1  | 2/2003  | Meadows               |

| 6,529,774 B1  | 3/2003  | Greene                |

| 6,597,954 B1  | 7/2003  | Pless et al.          |

| 6,606,521 B2  | 8/2003  | Paspa et al.          |

| 6,618,623 B1  | 9/2003  | Pless et al.          |

| 6,895,283 B2  | 5/2005  | Erickson et al.       |

| 6,920,359 B2  | 7/2005  | Meadows et al.        |

| 7,127,298 B1  | 10/2006 | He et al.             |

| 7,319,906 B2  | 1/2008  | Kuzma et al.          |

| 7,437,197 B2  | 10/2008 | Harris et al.         |

| 7,499,755 B2  | 3/2009  | Cross, Jr.            |

| 7,676,273 B2  | 3/2009  | Goetz et al.          |

|               |         |                       |

|               | 6/2010  | Swoyer et al.         |

| 7,769,461 B2  | 8/2010  | Whitehurst et al.     |

| 7,894,905 B2  | 2/2011  | Pless et al.          |

| 8,027,735 B1  | 9/2011  | Tziviskos et al.      |

| 8,030,798 B2  | 10/2011 | Seligman              |

| 8,140,152 B2  | 3/2012  | John et al.           |

| 8,165,678 B2  | 4/2012  | Forsberg et al.       |

| 8,412,334 B2  | 4/2013  | Whitehurst et al.     |

| 8,504,163 B1  | 8/2013  | Meadows               |

| 8,509,876 B2  | 8/2013  | Karmarkar             |

| 8,538,545 B2  | 9/2013  | Meskens               |

| 8,543,212 B2  | 9/2013  | Merfeld et al.        |

| 8,634,909 B2  | 1/2014  | Zimmerling et al.     |

| 8,639,344 B2  | 1/2014  | Greenberg et al.      |

| 8,649,880 B1  | 2/2014  | Parker                |

| 8,718,779 B2  | 5/2014  | Whitehurst et al.     |

| 8,774,924 B2  | 7/2014  | Weiner                |

| 8,958,880 B2  | 2/2014  | De Giorgio            |

| 8,972,015 B2  | 3/2015  | Stack et al.          |

|               |         |                       |

| 9,020,589 B2  | 4/2015  | Torgerson             |

|               |         |                       |

| 9,095,699     | B2  | 8/2015  | Rosenberg et al.        |

|---------------|-----|---------|-------------------------|

| 9,101,732     | B2  | 8/2015  | Dadd et al.             |

| 2002/0116042  | A1  | 8/2002  | Boling                  |

| 2005/0075696  | A1* | 4/2005  | Forsberg A61N 1/3787    |

|               |     |         | 607/61                  |

| 2005/0102006  | A1* | 5/2005  | Whitehurst A61M 5/14276 |

|               |     |         | 607/46                  |

| 2005/0182470  | A1  | 8/2005  | Cross                   |

|               | Al  | 9/2005  | Erickson et al.         |

|               | Al  | 10/2006 | Whitehurst et al.       |

| 2006/0247754  |     | 11/2006 | Greenberg et al.        |

| 2006/0293723  |     | 12/2006 | Whitehurst et al.       |

|               | Al  | 3/2007  | Rooney et al.           |

|               | Al  | 5/2007  | Mann et al.             |

|               | Al  | 8/2007  | Stone et al.            |

| 2008/0039916  |     | 2/2008  | Colliou et al.          |

| 2008/0183253  |     | 7/2008  | Bly                     |

| 2008/0269716  |     | 10/2008 | Bonde                   |

| 2008/0300657  |     | 12/2008 | Stultz                  |

|               | Al  | 1/2009  | Skelton et al.          |

| 2009/0210028  |     | 8/2009  | Rigaux                  |

|               | Al  | 12/2009 | Dadd                    |

| 2010/0161004  |     | 6/2010  | Najafi                  |

| 2010/0274313  |     | 10/2010 | Boling et al.           |

|               | Al  | 12/2010 | Digiore et al.          |

| 2011/0009925  |     | 1/2011  | Leigh et al.            |

|               | Al  | 4/2011  | Davis et al.            |

|               | Al  | 5/2011  | Degiorgio et al.        |

| 2011/0172736  |     | 7/2011  | Gefen et al.            |

| 2012/0078327  |     | 3/2012  | Sloan et al.            |

|               | Al  | 5/2012  | Forsell                 |

| 2012/0215218  |     | 8/2012  | Lipani                  |

| 2012/0213218  |     | 11/2012 | Dinsmoor et al.         |

|               | Al  | 11/2012 | Gerber et al.           |

| 2012/02/7823  |     | 4/2012  | Mashiach                |

| 2013/0085561  |     | 4/2013  | Mashiach                |

| 2013/0197613  |     | 8/2013  | Kelly                   |

| 2013/0197013  |     | 8/2013  | Hansen                  |

|               | Al  | 9/2013  | Baudino                 |

| 2013/0282086  |     | 10/2013 | McDonald et al.         |

| 2013/0232030  |     | 12/2013 | Lotfi                   |

| 2013/0333318  |     | 1/2013  | Zimmerling              |

| 2014/0070808  |     | 3/2014  | Reykowski G01R 33/3657  |

| 2014/00/0808  | AI  | 5/2014  |                         |

| 2014/01/12/20 |     | 5/2014  | 324/309                 |

| 2014/0142669  |     | 5/2014  | Cook et al.             |

| 2014/0148883  |     | 5/2014  | Stack et al.            |

| 2014/0222125  |     | 8/2014  | Glenn et al.            |

| 2014/0303685  | A1  | 10/2014 | Rosenberg et al.        |

| 2014/0343626  | A1  | 11/2014 | Thenuwara et al.        |

| 2015/0025613  | A1  | 1/2015  | Nyberg, II et al.       |

| 2015/0087892  | A1  | 3/2015  | Tourrel et al.          |

| 2015/0157862  | A1* | 6/2015  | Greenberg A61B 5/6868   |

|               |     |         | 607/60                  |

| 2016/0008602  | A1* | 1/2016  | Perryman A61N 1/36125   |

|               |     |         | 607/61                  |

|               |     |         | 00//01                  |

|               |     |         |                         |

#### OTHER PUBLICATIONS

Weiner RL and Reed KL. Peripheral neurostimulation for control of intractable occipital neuralgia. Neuromodulation: Journal of the International Neuromodulation Society. Jan. 1, 1999; 2: 217-21. Goadsby PJ and Spencer T. Current practice and future directions in

the prevention and acute management of migraine. The Lancet Neurology. Jan. 1, 2010; 9: 285-98. Dodick DW. Occipital nerve stimulation for chronic cluster head-

ache. Advanced Studies in Medicine. Jan. 1, 2003; 3: S569-S71. Saper JR, Dodick DW, Silberstein SD, McCarville S, Sun M and Goadsby PJ. Occipital nerve stimulation for the treatment of intractable chronic migraine headache: ONSTIM feasibility study. Cephalalgia: an international journal of headache. Jan. 1, 2011; 31:271-85.

Silberstein S, Dodick DW, Reed KL, et al. Safety and efficacy of peripheral nerve stimulation of the occiptial nerves for the management of chronic migraine. Cephalalgia: an international journal of headache. Jan. 1, 2012.

## (56) **References Cited**

## OTHER PUBLICATIONS

Slavin KV, Colpan ME, Munawar N, Wess C and Nersesyan H. Trigeminal and occipital peripheral nerve stimulation for craniofacial pain: a single-institution experience and review of the literature. Neurosurgical focus. Jan. 1, 2006; 21: E5.

Schwedt TJ, Dodick DW, Hentz J, Trentman TL and Zimmerman RS. Occipital nerve stimulation for chronic headache—long-term safety and efficacy. Cephalagia: an international journal of head-ache. Jan. 1, 2007; 27: 153-7.

Reed KL, Black SB, Banta CJ, 2nd and Will KR. Combined occipital and supraorbital neurostimulation for the treatment of chronic migraine headaches: initial experience. Cephalalgia: an international journal of headache. Jan. 1, 2010; 30: 260-71.

Reed KL, Will KR, Chapman J and Richter E. Combined occipital and supraorbital neurostimulation for chronic migraine headaches [abst]. 15th Congress of the International Headache Society. Berlin, Germany: Cephalalgia, Jan. 1, 2011, p. 98-99.

Lipton RB, Goadsby PJ, Cady RK, et al. PRISM study: occipital nerve stimulation for treatment-refractory migraine (p abs). Cephalalgia: an international journal of headache. Jan. 1, 2009; 29: 30.

Reed KL. Peripheral neuromodulation and headaches: history, clinical approach, and considerations on underlying mechanisms. Current pain and headache reports. Jan. 1, 2012; 17: 25-35.

Mueller OM, Gaul C, Katsarava Z, Diener HC, Sure U and Gasser T. Occipital nerve stimulation for the treatment of chronic cluster headache—lessons learned from 18 months experience. Central European neurosurgery. Jan. 1, 2011; 72: 84-9.

Medtronic, Inc. Peripheral Nerve Stimulation: Percutaneous Lead Implantation Guide for Treatment of Chronic Pain; Jan. 1, 1999.

\* cited by examiner

U.S. Patent

Sheet 4 of 37

US 9,498,635 B2

FIG. 6

FIG. 8

FIG. 10

Sheet 20 of 37

**U.S.** Patent

Nov. 22, 2016

US 9,498,635 B2

**U.S.** Patent

**U.S.** Patent

Nov. 22, 2016

Sheet 27 of 37

FIG. 22B

FIG. 23A

# **IMPLANTABLE HEAD LOCATED RADIOFREOUENCY COUPLED NEUROSTIMULATION SYSTEM FOR HEAD** PAIN

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a Continuation-in-Part of U.S. patent application Ser. No. 14/879,943, filed Oct. 9, 2015, entitled SURGICAL METHOD FOR IMPLANTABLE HEAD MOUNTED NEUROSTIMULATION SYSTEM FOR HEAD PAIN, the specification of which is incorporated by reference herein in its entirety. U.S. patent application Ser. 15 No. 14/879,943 is a Continuation-in-Part of U.S. patent application Ser. No. 14/717,912, filed May 20, 2015, entitled IMPLANTABLE HEAD MOUNTED NEUROSTIMULA-TION SYSTEM FOR HEAD PAIN, the specification of which is incorporated by reference herein in its entirety. U.S. 20 patent application Ser. No. 14/717,912 is a Continuation of U.S. patent application Ser. No. 14/460,139, filed Aug. 14, 2014, entitled IMPLANTABLE HEAD MOUNTED NEU-ROSTIMULATION SYSTEM FOR HEAD PAIN, now issued as U.S. Pat. No. 9,042,991, the specification of which 25 ing features. The system may include the disposition of a is incorporated by reference herein in its entirety. U.S. patent application Ser. No. 14/460,139 claims benefit of U.S. Provisional Application No. 61/894,795, filed Oct. 23, 2013, entitled IMPLANTABLE HEAD MOUNTED NEURO-STIMULATION SYSTEM FOR HEAD PAIN, the specifi- 30 cation of which is incorporated by reference herein in its entirety.

# TECHNICAL FIELD

The present disclosure relates to implantable neurostimulation systems and methods of treating migraine headaches and other forms of chronic head pain.

### BACKGROUND OF THE INVENTION

Neurostimulation systems comprising implantable neurostimulation leads are used to treat chronic pain. Conventional implantable peripheral neurostimulation leads are designed for placement in the spinal canal as part of a spinal 45 cord stimulation system, and for the therapeutic purpose of treating various forms of chronic back and extremity pain. Implantable neurostimulation systems may either be powered by an internal battery or by an external power source coupled to the internal unit by a radiofrequency interface. 50

### SUMMARY OF THE INVENTION

In various implementations, an implantable headmounted, radiofrequency-coupled, unibody peripheral nerve 55 stimulation system may be configured for implantation of substantially all electronics, except for an on-site battery, at or near the implanted electrodes on the skull. The system may include an implantable pulse generator (IPG) from which two neurostimulating leads may extend to a length 60 sufficient to provide therapeutic neurostimulation unilaterally over the frontal, parietal and occipital regions of the hemicranium. The IPG may have a component, or extension, containing an internal radiofrequency receiver, the purpose of which is to couple to an external power source and control 65 unit. The system may be operable to provide medically acceptable therapeutic neurostimulation to multiple regions

of the head, including the frontal, parietal and occipital regions of the hemicranium substantially simultaneously.

Each of the leads may include an extended lead body; a plurality of surface metal electrodes disposed along the lead body, which may be divided into two or more electrode arrays; and a plurality of internal electrically conducting metal wires running along at least a portion of the length of the lead body and individually connecting an internal circuit of the IPG to individual surface metal electrodes. The extended lead body may comprise a medical grade plastic.

Implementations may include one or more of the following features. The IPG may be of proper aspect ratio with respect to the specific site of intended implantation in the head, such as an area posterior to and/or superior to the ear. The IPG may include an antenna coil and an application specific integrated circuit (ASIC). The IPG may be configured for functionally connecting with an external radiofrequency unit.

Implementations may include one or more of the following features. A neurostimulating lead may not include a central channel for a stylet. A neurostimulating lead may have a smaller diameter than conventional leads.

Implementations may include one or more of the followsufficient plurality of surface electrodes over a sufficient linear distance along the neurostimulating leads to enable medically adequate therapeutic stimulation across multiple regions of the head, including the frontal, parietal, and occipital region of the hemicranium substantially simultaneously. The extended array of surface electrodes may be divided into two or more discrete terminal surface electrode arrays. The linear layout of the multiple surface electrode arrays may include at least one array positioned over the frontal region, at least one array positioned over the parietal region, and at least one array positioned over the occipital region. Specific intra-array design features may include variations in the specific number of electrodes allotted to each group; the shape of the electrodes, e.g., whether the 40 electrodes are cylindrical or flattened; the width of each electrode within each array, and the linear distance intervals of separation of the electrodes within each array.

Various implementations may include a plurality of connection ports that can be connected with a plurality of leads and thus allow for attaching additional leads.

The external radiofrequency unit may be operable to perform various functions including recharging the rechargeable battery, diagnostically evaluating the IPG, and programming the IPG.

In various implementations, methods of treating chronic pain may include methods of treating chronic head and/or face pain of multiple etiologies, including migraine headaches; and other primary headaches, including cluster headaches, hemicrania continua headaches, tension type headaches, chronic daily headaches, transformed migraine headaches; further including secondary headaches, such as cervicogenic headaches and other secondary musculoskeletal headaches.

In various implementations, methods of treating chronic pain may include methods of treating head and/or face pain of multiple etiologies, including neuropathic head and/or face pain, nociceptive head and/or face pain, and/or sympathetic related head and/or face pain.

In various implementations, methods of treating chronic pain may include methods of treating head and/or face pain of multiple etiologies, including greater occipital neuralgia, as well as the other various occipital neuralgias, supraorbital neuralgia, auroiculotemporal neuralgia, infraorbital neuralgia, and other trigeminal neuralgias, and other head and face neuralgias.

The details of one or more implementations are set forth in the accompanying drawings and the description below. 5 Other features, objects, and advantages of the implementations will be apparent from the description and drawings.

In certain aspects, a method is provided for controlling power delivery from an external power transfer system (EPTS) to at least one implantable neurostimulation system 10 (INS). In some embodiments, the method includes driving a first transmit coil within the EPTS with a resonant current having a peak magnitude, using a transmit coil driver circuit within the EPTS. The method also includes receiving, using a receive coil within a first INS tuned to the resonant 15 frequency of the first transmit coil, power transferred from the first transmit coil, and coupling the received power to a regulator circuit within the first INS which is configured to provide an electrode current to an electrode driver circuit within the first INS for a plurality of electrodes therewithin. 20 The method further includes monitoring the regulator circuit within the first INS to determine whether the received power coupled thereto is sufficient to achieve current regulation of the regulator circuit within the first INS. The method further includes communicating a message to the EPTS using a 25 back telemetry transmit circuit within the first INS, the message requesting a change in power transfer from the EPTS based upon the regulator circuit determination, and receiving, using a back telemetry receive circuit within the EPTS, the message communicated by the first INS. The 30 method also includes adjusting the transmit coil driver circuit within the EPTS to change the peak magnitude of the resonant current, corresponding to the requested change in power transfer.

In some embodiments, the method also includes a message which includes a request to increase power transfer from the EPTS if the regulator circuit within the first INS is not achieving current regulation, and includes a corresponding change in the peak magnitude of the resonant current which includes an increase in peak magnitude. Some 40 embodiments will additionally include adjusting the transmit coil driver circuit within the EPTS to decrease the peak magnitude of the resonant current, if no message requesting an increase in power transfer from the EPTS has been received from the first INS for at least a certain period of 45 time.

In some embodiments, the message includes a request to decrease power transfer from the EPTS if the regulator circuit within the first INS is achieving current regulation, and the corresponding change in the peak magnitude of the 50 resonant current includes a decrease in the peak magnitude.

In some embodiments, the monitoring the regulator circuit within the first INS is performed under control of a state machine circuit within the first INS, and the communicating a first message to the EPTS is performed under control of an 55 instruction-based processor within the first INS. In some embodiments, the state machine circuit within the first INS is configured to wake-up the instruction-based processor within the first INS, in the event the instruction-based processor is not already awake, to communicate the first 60 message.

In some embodiments, monitoring the regulator circuit within the first INS includes comparing the electrode current provided by the regulator circuit within the first INS against a prescribed electrode current for the electrode driver circuit 65 within the first INS corresponding to a stimulation configuration programmed therein, and determining that the regu4

lator circuit is achieving current regulation if the electrode current is greater than or equal to the prescribed electrode current. In some embodiments, comparing the electrode current against the prescribed electrode current is performed under control of a state machine circuit within the first INS.

In some embodiments, coupling the received power to a regulator circuit within the first INS includes rectifying a current induced on the receive coil, to generate a rectified voltage on an input node of the regulator circuit within the first INS. In some embodiments, monitoring the regulator circuit within the first INS includes monitoring an input voltage and an output voltage of the regulator circuit within the first INS, and determining that the regulator circuit is achieving current regulation if a voltage differential between the input voltage and the output voltage exceeds a predetermined value.

In some embodiments, the method further includes detuning the receive coil within the first INS, using a de-tuning circuit within the first INS, to substantially inhibit power transfer from the EPTS to the first INS.

In some embodiments, the regulator circuit within the first INS is further configured to provide a charging current to a charge storage device within the first INS. In certain of these embodiments, monitoring the regulator circuit within the first INS includes comparing the electrode current provided by the regulator circuit within the first INS against a prescribed electrode current for the electrode driver circuit within the first INS corresponding to a stimulation configuration programmed therein, comparing the charging current provided by the regulator circuit within the first INS against a predetermined charging current, and determining that the regulator circuit is achieving current regulation if the electrode current is greater than or equal to the prescribed electrode current, and the charging current is greater than or equal to the predetermined charging current. In certain of these embodiments, the charge storage device is a supercapacitor.

In some embodiments, the method further includes driving, using the transmit coil driver circuit within the EPTS, the resonant current through a second transmit coil coupled in series with the first transmit coil within the EPTS; receiving, using a receive coil within a second INS tuned to the resonant frequency of the second transmit coil, power transferred from the second transmit coil; coupling the received power within the second INS to a regulator circuit within the second INS which is configured to provide an electrode current to an electrode driver circuit within the second INS for a plurality of electrodes therewithin; monitoring the regulator circuit within the second INS to determine whether the received power coupled thereto is sufficient to achieve current regulation of the regulator circuit within the second INS; communicating a message from the second INS to the EPTS using a back telemetry transmit circuit within the second INS, said message requesting a change in power transfer from the EPTS based upon said regulator circuit determination for the second INS; receiving, using the back telemetry receive circuit within the EPTS, the third message communicated by the second INS; and adjusting the transmit coil driver circuit within the EPTS to change the peak magnitude of the resonant current, corresponding to the requested change in power transfer conveyed in the message communicated by the second INS.

In some embodiments, the method further includes adjusting the transmit coil driver circuit within the EPTS to decrease the peak magnitude of the resonant current, if no message requesting an increase in power transfer from the EPTS has been received from the first INS, and no message

requesting an increase in power transfer from the EPTS has been received from the second INS, for at least a certain period of time.

In some embodiments, the method further includes detuning the receive coil within the second INS, using a 5 de-tuning circuit within the second INS, to substantially inhibit power transfer from the EPTS to the second INS without inhibiting power transfer from the EPTS to the first INS.

In some embodiments, the first and second INSs are 10 head-located beneath a dermis layer, or skin, of a patient.

In another embodiment, a system is provided for controlling power delivery from an external power transfer system (EPTS) to at least one implantable neurostimulation system (INS). In some embodiments the system includes an EPTS 15 disposed outside a body, and at least one INS disposed beneath a dermis layer of the body. The EPTS includes a group of one or more transmit coils disposed in series, each corresponding to a respective INS; a transmit coil driver circuit operable to drive the group of one or more transmit 20 coils with a resonant current having a peak magnitude; and a back telemetry circuit operable to receive a message communicated by an INS. Each of said at least one INS respectively includes a receive coil tuned to the resonant frequency of the corresponding transmit coil and operable to 25 receive power transferred therefrom when in proximity thereto; a regulator circuit having an input to which the received power is coupled, and operable to provide on an output thereof an electrode current to an electrode driver circuit for a plurality of electrodes; a monitoring circuit 30 operable to determine whether the received power is sufficient to achieve current regulation of the regulator circuit; and a back telemetry circuit operable to communicate a message to the EPTS. Each respective INS is operable to communicate a respective message requesting a change in 35 power transfer from the EPTS based upon the respective regulator circuit determination; and the EPTS is operable to adjust the transmit coil driver circuit to change the peak magnitude of the resonant current, based upon respective messages from one or more respective INS.

In some embodiments, each respective message includes a request to increase power transfer from the EPTS if the respective regulator circuit is not achieving current regulation, and the EPTS is further operable to adjust the transmit coil driver circuit to increase the peak magnitude of the 45 resonant circuit, in response to receiving a respective message from any respective INS requesting an increase in power transfer.

In some embodiments, the EPTS is further operable to adjust the transmit coil driver circuit to decrease the peak 50 magnitude of the resonant current, if no respective message requesting an increase in power transfer from the EPTS has been communicated by any respective INS for at least a certain period of time.

In some embodiments, each respective message includes 55 a request to decrease power transfer from the EPTS if the respective regulator circuit is achieving current regulation, and the EPTS is further operable to adjust the transmit coil driver circuit to decrease the peak magnitude of the resonant current, in response to receiving a respective message from 60 every respective INS requesting a decrease in power transfer.

In some embodiments, the respective monitoring circuit within each respective INS is operable to compare the respective electrode current provided by the respective regulator circuit against a respective prescribed electrode current for the respective electrode driver circuit corresponding to a

stimulation configuration programmed therein, and determine that the respective regulator circuit is achieving current regulation if the respective electrode current is greater than or equal to the respective prescribed electrode current.

In some embodiments, each respective INS further includes a respective resonant rectifier circuit having an input coupled to the respective receive coil, and having an output coupled to the input of the respective regulator circuit. The respective resonant rectifier circuit is operable to generate on its respective output a rectified voltage. In some embodiments each respective INS may further include a respective de-tuning circuit coupled to the respective receive coil, being operable to de-tune the respective receive coil to inhibit power transfer from the EPTS to the respective INS.

In some embodiments, each respective INS further includes a respective charge storage device, and each respective regulator circuit is further operable to provide on a second output thereof a charging current to the respective charge storage device. In some embodiments each respective charge storage device may be a supercapacitor.

In some embodiments, each respective INS is head-located beneath the dermis layer of a patient.

In another embodiment, a neurostimulation system is provided including a power unit, which includes a variable power generator, a controller to control the output power level of the variable power generator, a power coupler for coupling power over a dermis layer, and a power source telemetry system for receiving information across a dermis laver for input to the controller; and an implantable neurostimulator including at least one neurostimulator lead with at least one array of stimulation electrodes, an electrode driver for driving the electrodes with a desired power, a power level detector for detecting the output power of the electrode driver, a neurostimulator power coupler for coupling power from over a dermis layer, a neurostimulator telemetry system for transmitting information across the dermis layer to the power source telemetry system, and a processor for determining the amount of power required from the power source as a power demand based on the output of the power 40 level detector and transmitting a request for a desired power level to the controller via the telemetry system in the power source; wherein the controller increases or decreases the power level delivered to the implantable neurostimulator as a function of determined power demand by the processor.

In some embodiments, the power unit and neurostimulator power couplers each include at least one coil. In some of these embodiments, the variable power generator generates alternating current power. Some embodiments further include a controller which varies the power generated by varying a voltage of the variable power generator. In some embodiments, the implantable neurostimulator further includes a charge storage device. In some embodiments, the power unit power coupler is inductively coupled to the neurostimulator power coupler. In some embodiments, the neurostimulator and the power unit telemetry system each communicate information across the dermis layer through the respective power unit and neurostimulator power couplers.

In another embodiment, a system is provided for driving an implantable neurostimulator lead having a plurality of electrodes disposed in at least one array, the system including an implantable pulse generator (IPG), which includes an electrode driver for driving the electrodes, a load system for determining load requirements of the IPG, an IPG power coupler for receiving power across a dermis layer for interface of the power with the electrode driver, and an IPG communication system for transmitting the load determined requirement of the IPG across the dermis layer. In this embodiment, the system also includes an external unit, which includes an external variable power generator, an external power coupler for coupling power across the dermis layer to the IPG power coupler, an external communication 5 system for receiving from the IPG communication system the determined load requirements, and a controller for varying the power level of the variable generator as a function of the received determined load requirements of the IPG. 10

In some embodiments, the electrode driver drives the electrodes with a constant current. In some embodiments, the load system further includes a detector for detecting power delivered to the electrodes and a processor for determining the necessary power from the external unit required 15 by the electrode driver as the determined load requirements of the IPG. In some embodiments, the electrode driver delivers a predetermined constant current. In some of these embodiments, the predetermined load requirement includes at least enough power from the external unit to provide the 20 predetermined constant current from the electrode driver. In some embodiments, the IPG also includes a charge storage device. In some embodiments, the IPG is head-located beneath the dermis layer of a patient. In some embodiments, the IPG communication system and the external communi- 25 cation system each include at least one coil.

In another embodiment, the system is for driving a plurality of implantable neurostimulator leads, each lead having an associated plurality of electrodes disposed in at least on array on the lead. The system includes at least two 30 implantable pulse generators (IPGs), with each IPG including an electrode driver for driving the electrodes associated with the IPG, a load system for determining load requirements of the IPG, an IPG power coupler for receiving power across a dermis layer for interface of the power with the 35 electrode driver of the IPG, and an IPG communication system for transmitting the load determined requirement of the IPG across the dermis layer. The system also includes an external unit, which includes an external variable power generator, and external power coupler for coupling power 40 across the dermis layer to the IPG power couplers, and external communication system for receiving from the IPG communication systems the respective determined load requirements, and a controller for varying the power level of the variable power generator as a function of the received 45 determined load requirements of the IPG with the greatest load requirement.

In some embodiments, the communication systems of the IPGs are operable to transmit load requirements to the external communication system independently of the com- 50 munication systems of the other IPGs. In some embodiments the IPG communication systems transmit the load determined requirements to the external unit communication system inductively. In some embodiments, the IPG power couplers are for receiving levels of power across a dermis 55 layer that are independent of the levels of power received by the power couplers of the other IPGs. In some embodiments, at least one of the IPGs also includes a charge storage device.

The foregoing is a summary and thus contains, by neces- 60 sity, simplifications, generalizations and omissions of detail. The details of various implementations are set forth in the accompanying drawings and the description below. Consequently, those skilled in the art will appreciate that the foregoing summary is illustrative only and is not intended to 65 be in any way limiting of the invention. It is only the claims, including all equivalents, in this or any non-provisional

application claiming priority to this application, that are intended to define the scope of the invention(s) supported by this application.

# BRIEF DESCRIPTION OF THE DRAWINGS

For a more complete understanding, reference is now made to the following description taken in conjunction with the accompanying Drawings in which:

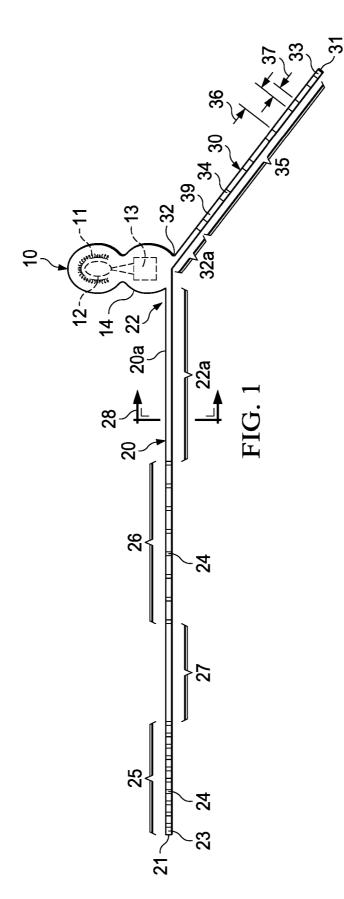

FIG. 1 depicts a side view of a full Head-Mounted, Unibody Radiofrequency-Coupled Neurostimulator System for migraine and other head pain. The system features an implantable pulse generator (IPG) from which two neurostimulating leads extend—a Frontal-Parietal Lead (FPL) and an Occipital Lead (OL). Each lead includes a plurality of electrodes in a distribution and over a length to allow full unilateral coverage of the frontal, parietal, and occipital portions of the head. The IPG contains all electronics, including an Application Specific Integrated Circuit (ASIC) and an RF Receiver Coil that is capable of an RF couple to an External Power Source and Programming Unit;

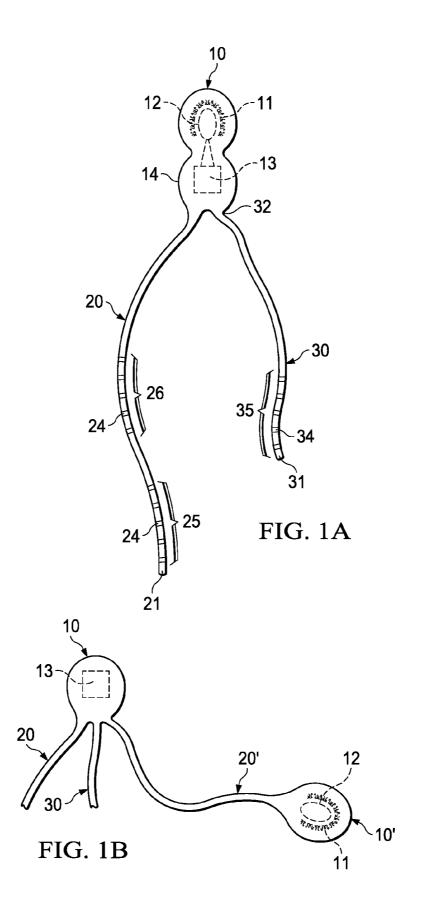

FIG. 1A illustrates an embodiment of the IPG 10 and the various configurations of the lead;

FIG. 1B illustrates an embodiment of the IPG 10 and the various configurations of the lead;

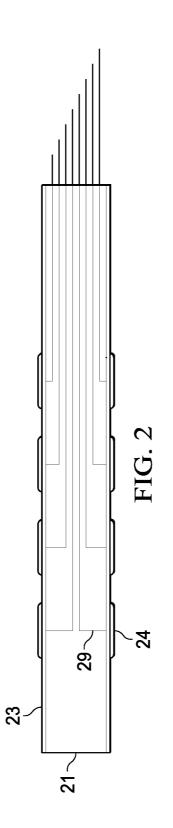

FIG. 2 depicts a side view of a Frontal Electrode Array (FEA) with Internal Wires. The FEA is disposed over the distal portion (such as 8-10 cm) of the FPL, which anatomically places it over the frontal region, and specifically over the supraorbital nerve and other adjacent nerves of the region. In general the layout, disposition and connections of the Internal Wires and Surface Electrodes disposed over the Parietal Electrode Array (PEA) and the Occipital Electrode Array (OEA) are the same as that depicted for the FEA;

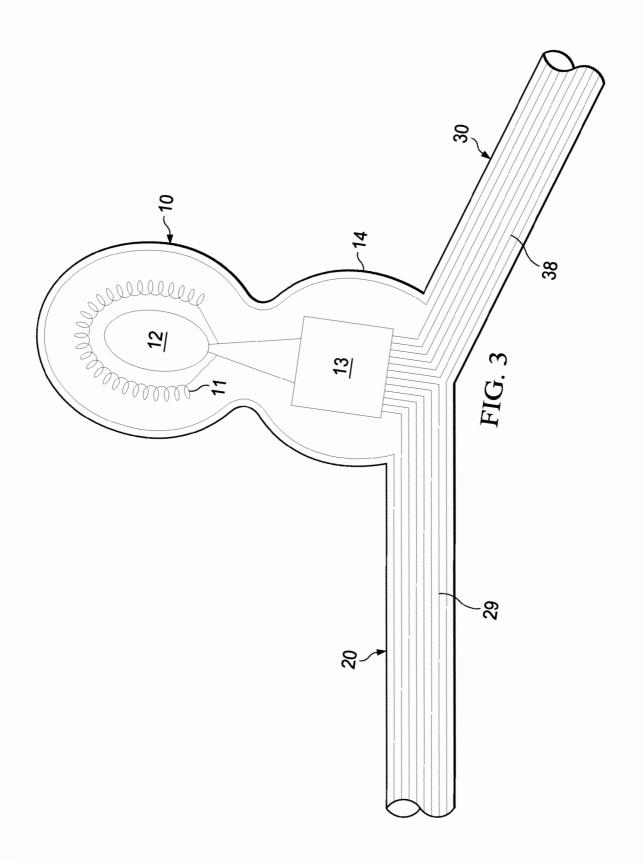

FIG. 3 depicts a side view of an IPG, along with its enclosed ASIC, RF Receiver Coil, and Internal Magnet, along with the Internal Wires exiting from the IPG's Internal Circuit enroute to the Surface Electrodes disposed over the FPL and the OL;

FIG. **3**A depicts a more detailed view of the internal structure of an IPG;

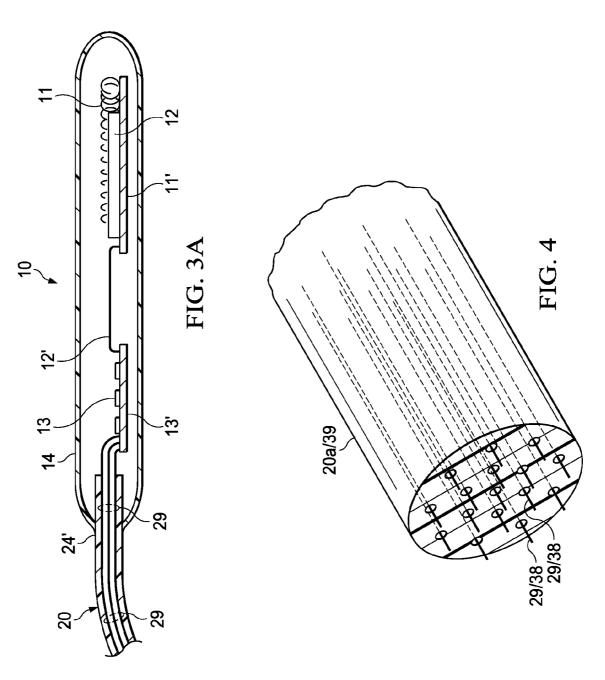

FIG. **4** depicts a cross-sectional view of a Lead Central Body comprising a Cylindrical Lead Body (with Internal Wires) between the IPG Internal Circuit and the Lead Surface Electrodes;

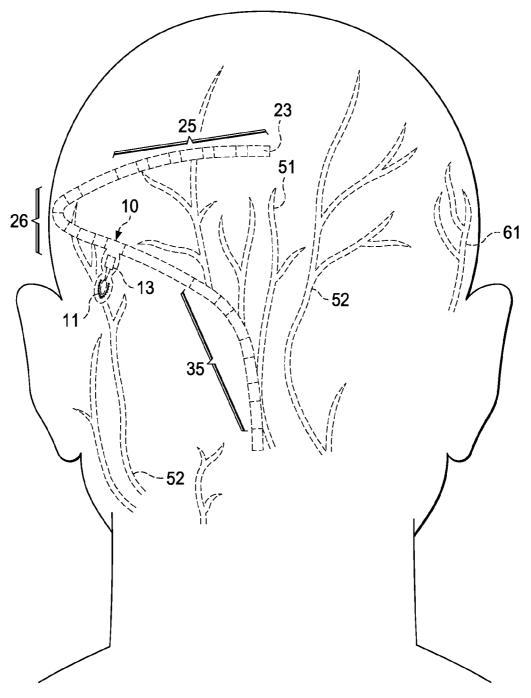

FIG. **5** depicts a rear view of a Head with a full Head-Located Neurostimulator System In-Situ. Prominent here is the OL depicted passing from the IPG caudally and medially across the occipital region, whereby the OEA is disposed in a fashion to cross over and cover the major associated nerves—primarily the greater occipital nerve, but typically including the lessor and/or third occipital nerve as well. Also depicted are the PEA and the FEA of the FPL as they cross and cover the primary nerves of the Parietal Region, including the auriculo-temporal nerve, and the Frontal Region, including the supraorbital nerve. Also depicted is the IPG with its Internal Circuit, Internal RF Receiver Coil, and ASIC;

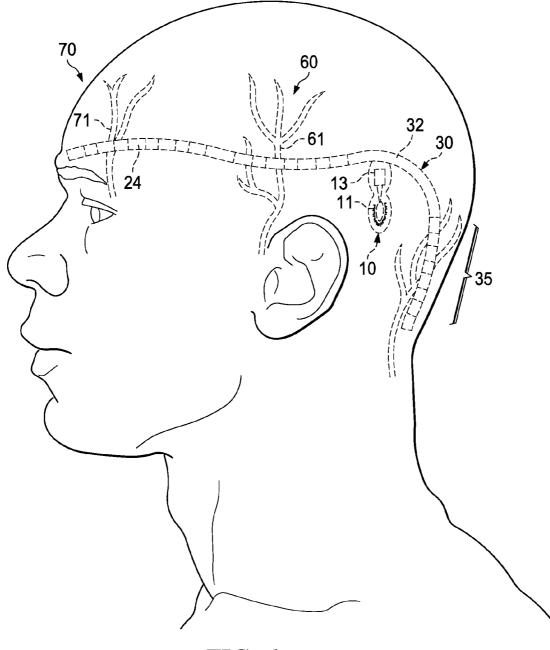

FIG. 6 depicts a side view of a Head with a full Head-Located, Unibody Radiofrequency-Coupled Neurostimulator System In-Situ. Prominent here is the PEA, as it covers a portion of the Parietal Region 60 and the major associated nerves, including the auriculo-temporal nerve 61 as well as other adjacent cutaneous nerves. The frontal region of the head and supraorbital nerve 71 are also depicted. Also depicted are the courses of the distal portion of the FPL and the OL, as they pass over and cover the associated nerves of

50

the Frontal (Supraorbital) and Occipital Regions. Also depicted is the IPG including its Internal Circuit, ASIC, and **RF** Receiver Coil:

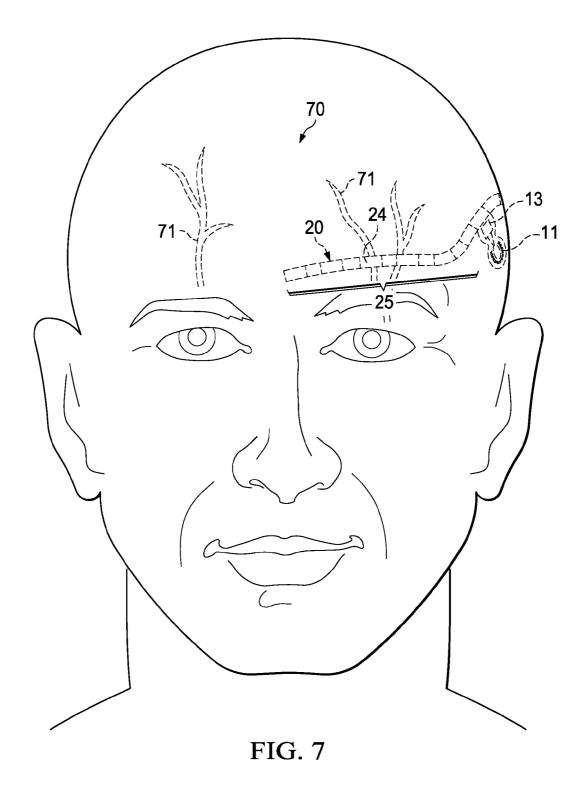

FIG. 7 depicts a front view of a Head with a full Head-Located, Unibody Radiofrequency-Coupled Neurostimulator System In-Situ. Prominent here is the FEA, as it covers a portion of the Frontal (Supraorbital) Region and the major associated nerves-primarily the supraorbital nerve, but also commonly the greater trochlear nerve, as well as adjacent nerves. Also depicted is the course of the parietal portion of the FL. Also depicted is the IPG including its Internal Circuit, ASIC, and RF Receiver Coil;

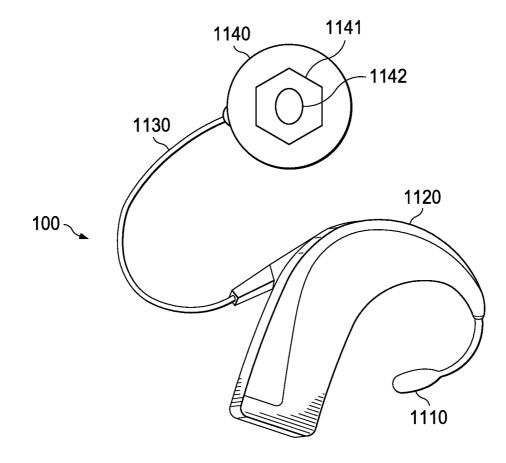

FIG. 8 depicts a side view of the External "Behind the Ear" Assembly. Prominent here is the IPG with its IPG including its Internal Circuit, ASIC, and RF Receiver Coil. The External Assembly includes the External Earl Clip, the Behind-the-Ear Electronics and Battery Component, the External Coil Lead, and the External RF Coil Plastic Housing, which contains the External RF Coil and External RF 20 Magnet;

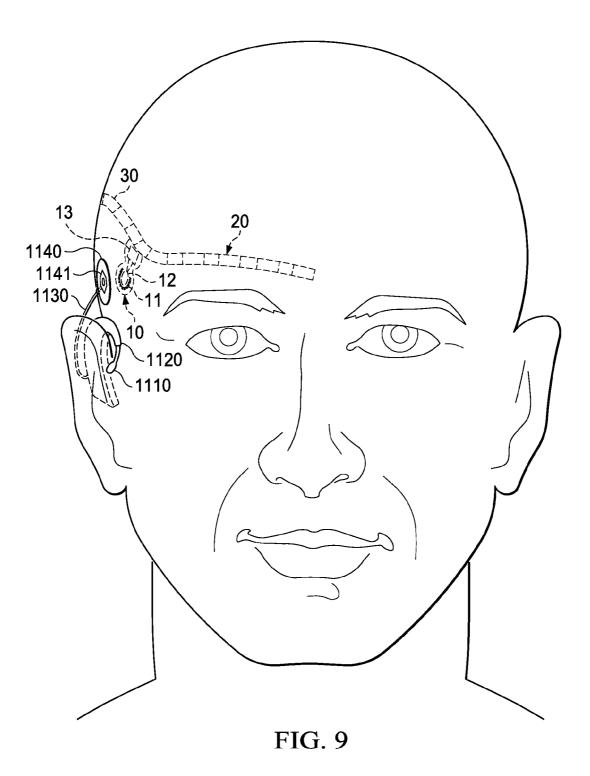

FIG. 9 depicts right oblique front view of a head with a full Head-Located, Unibody Radiofrequency-Coupled Neurostimulator System In-Situ, along with an External "Behind the Ear" Assembly. Prominent here is the IPG with its IPG 25 circuit and telemetry/de-tune circuit, such as those shown in including its Internal Circuit, ASIC, and RF Receiver Coil. The External Assembly includes the External Earl Clip, the Behind-the-Ear Electronics and Battery Component, the External Coil Lead, and the External RF Coil Plastic Housing, which contains the External RF Coil and External RF 30 Magnet;

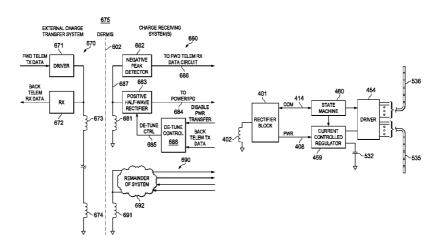

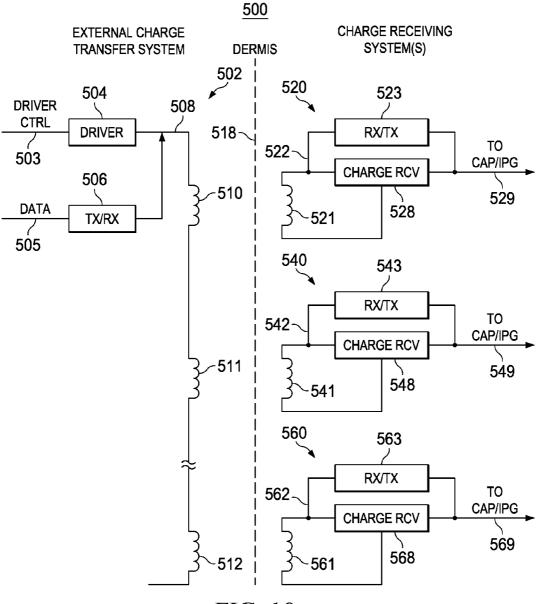

FIG. 10 is a block diagram of a system that provides for independent charge transfer and communication with multiple implanted devices, in accordance with some embodiments of the invention;

FIG. 11 is a block diagram of a system depicting the de-tuning of a receive coil within an implanted device to selectively turn off charging, in accordance with some embodiments of the invention;

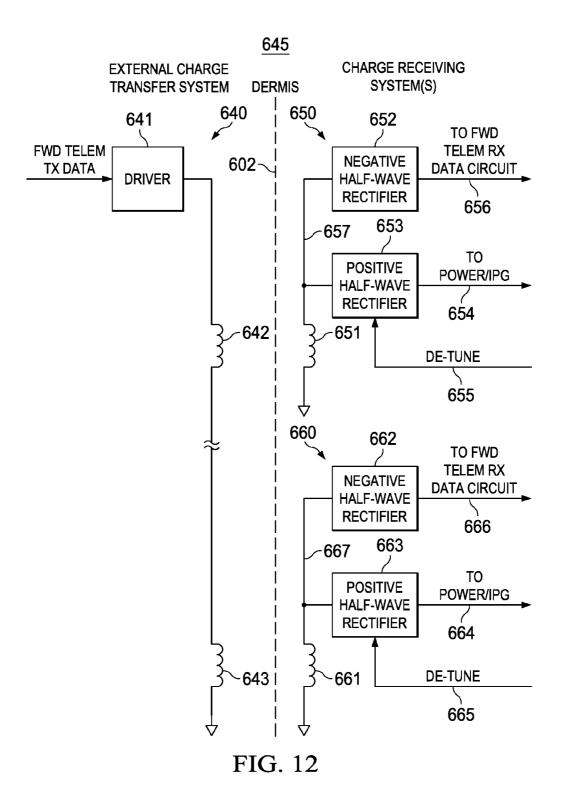

FIG. 12 is a block diagram of a system which provides for 40 data communication (forward telemetry) and power transmission to an implanted device using opposite polarity half-wave rectified signals received by the implanted device, in accordance with some embodiments of the invention;

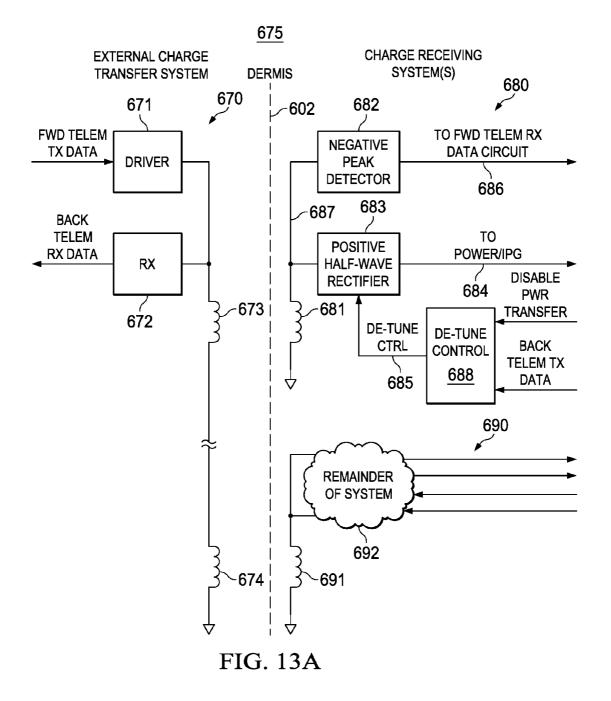

FIG. 13A is a block diagram of a system which provides 45 for bi-directional communication with an implanted device, and particularly illustrates passive communication from an implanted device (back telemetry) when the receive coil is de-tuned, in accordance with some embodiments of the invention:

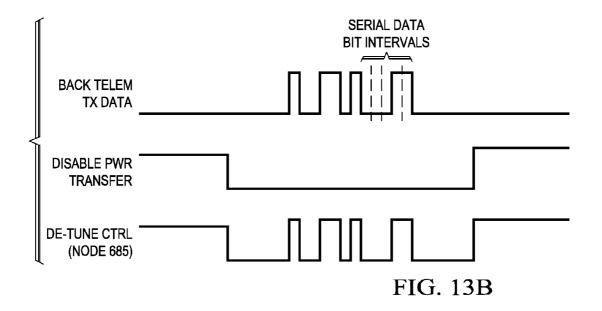

FIG. 13B illustrates voltage waveforms of selected signals depicted in the embodiment shown in FIG. 13A;

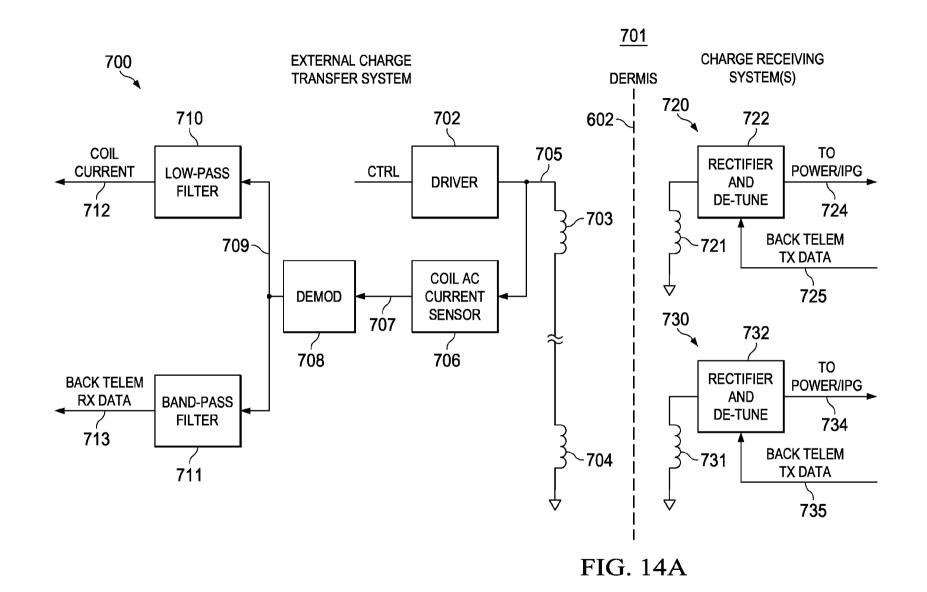

FIG. 14A is a block diagram of a system which includes charge transfer coil (or "transmit coil") current sensing circuitry to determine back telemetry data received from an 55 implanted device, and to determine de-tuning of an implanted device coil, in accordance with some embodiments of the invention:

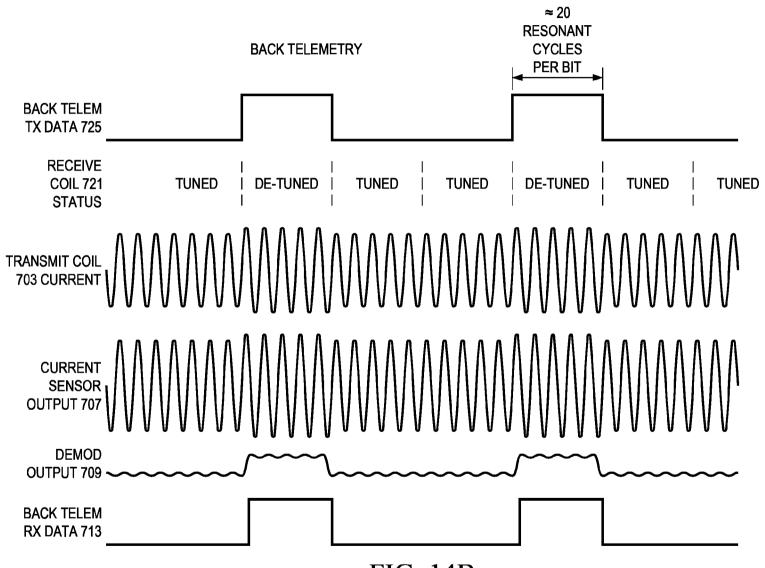

FIG. 14B illustrates voltage waveforms of selected signals depicted in the embodiment shown in FIG. 14A;

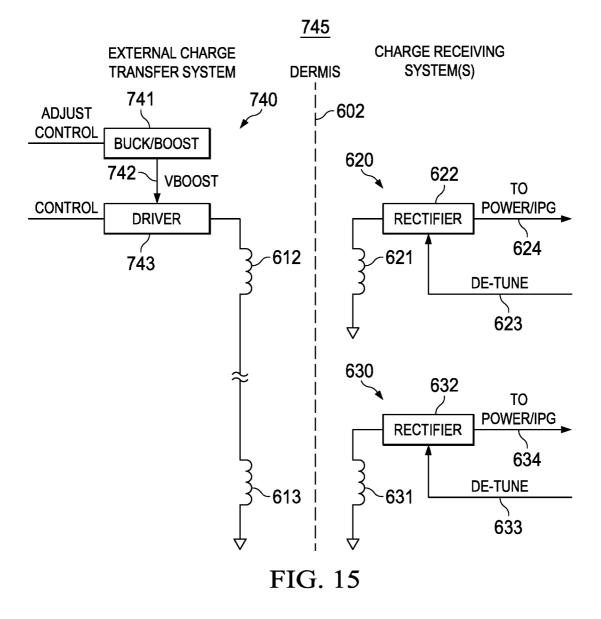

FIG. 15 is a block diagram of a system which provides for adjustable transmitted power to improve power efficiency within an implanted device, in accordance with some embodiments of the invention;

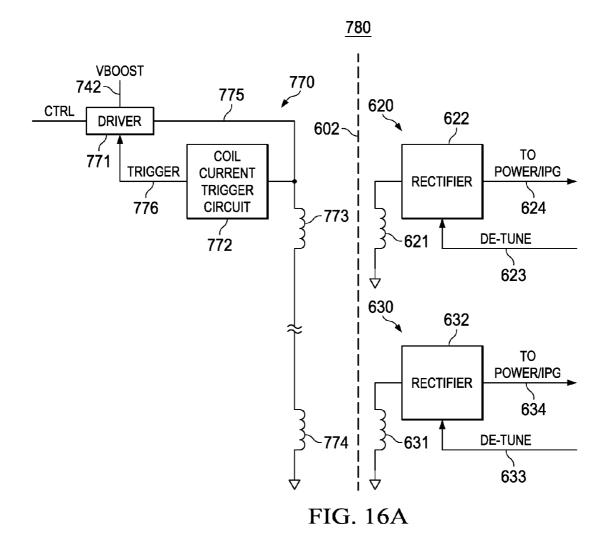

FIG. 16A is a block diagram of a system which includes 65 feedback excitation control of a resonant coil driver amplifier, in accordance with some embodiments of the invention.

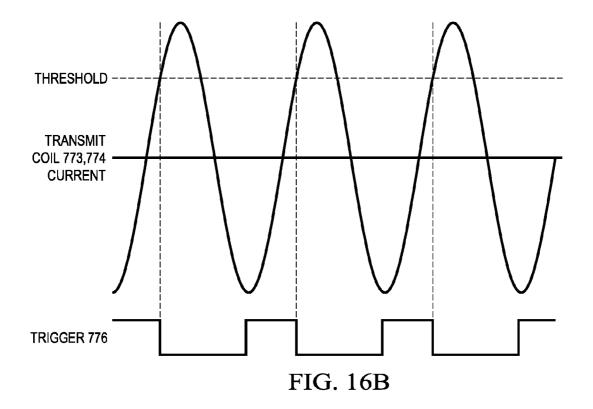

FIG. 16B illustrates voltage waveforms of selected signals depicted in the embodiment shown in FIG. 16A;

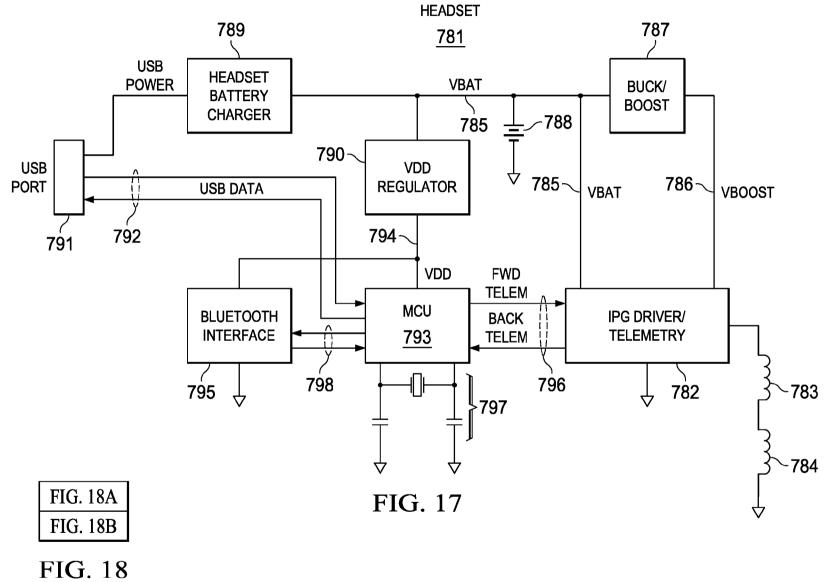

FIG. 17 is a block diagram of a headset that includes an external charge transfer system for two implanted devices, in accordance with some embodiments of the invention;

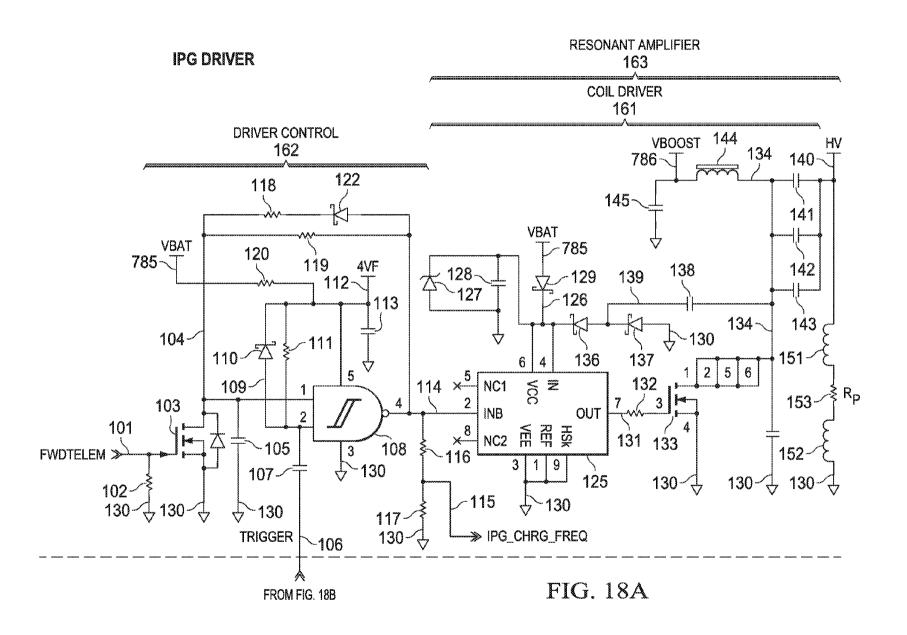

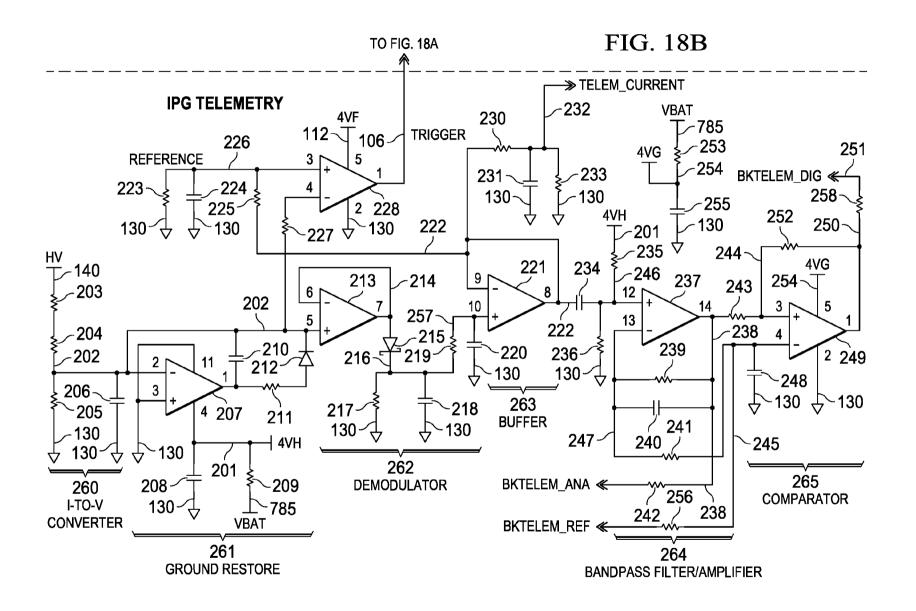

FIG. 18, which includes FIGS. 18A and 18B, is a schematic diagram of an exemplary IPG driver and telemetry circuitry block, such as that shown in FIG. 17, in accordance with some embodiments of the invention;

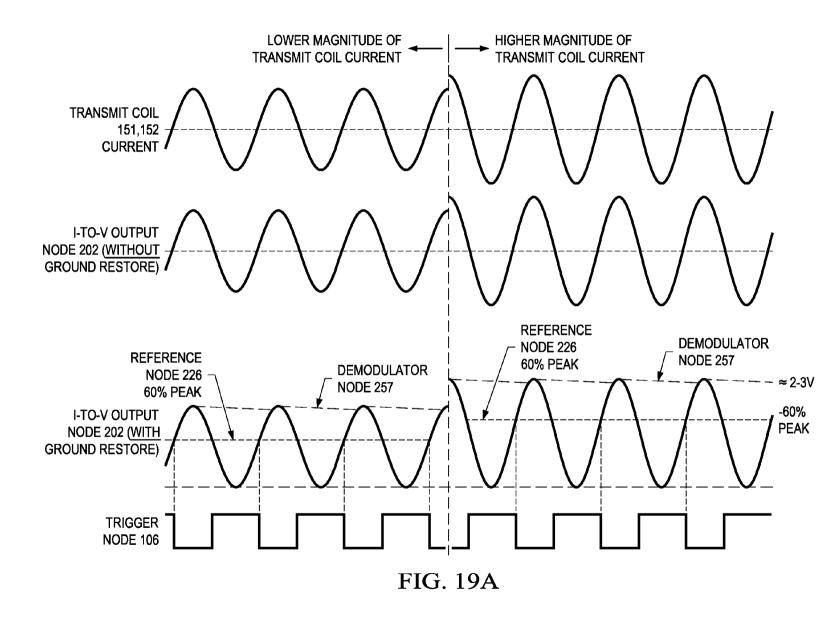

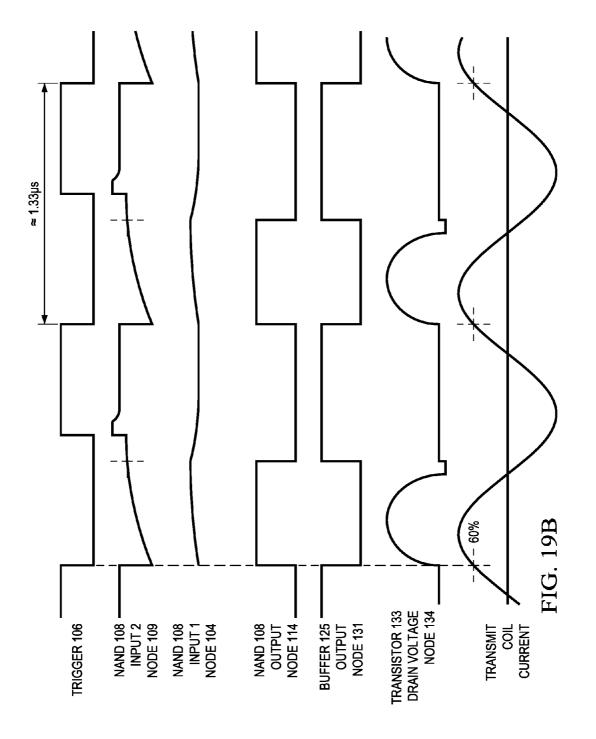

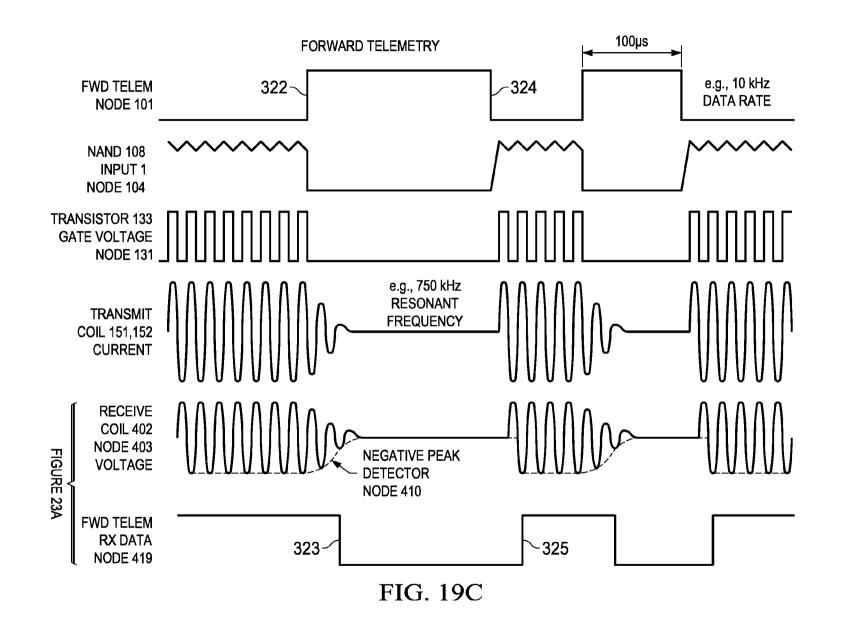

FIGS. 19A, 19B, and 19C illustrate voltage waveforms of selected signals depicted in the embodiment shown in FIG. 18 and FIG. 23A;

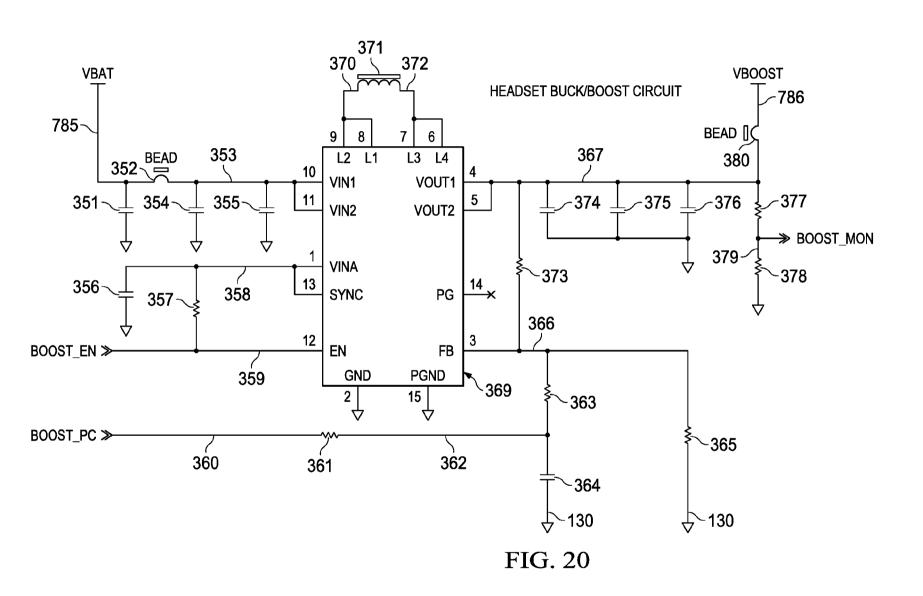

FIG. 20 is a schematic diagram of an exemplary headset buck/boost voltage generator circuit, such as that shown in 15 FIG. 8, in accordance with some embodiments of the invention:

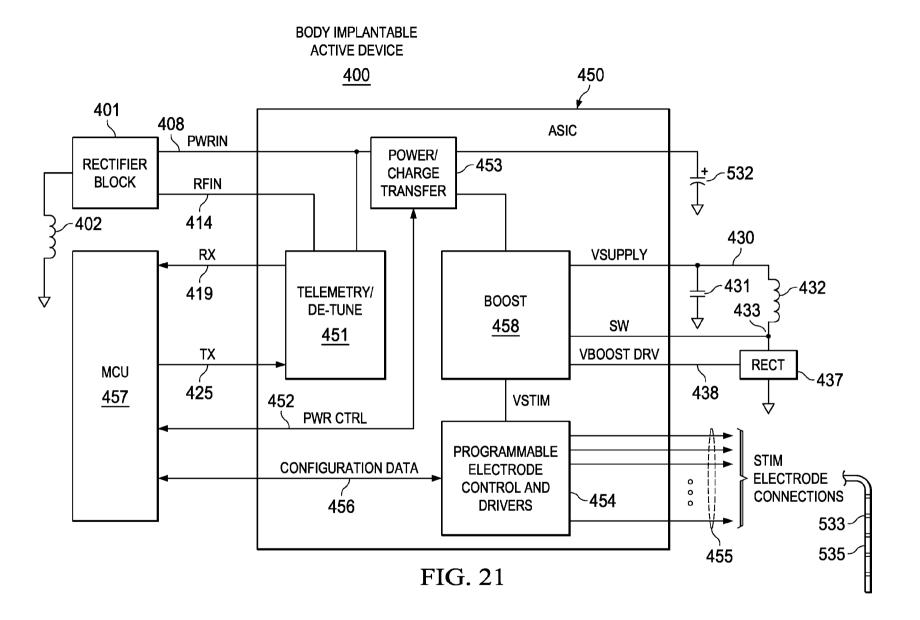

FIG. 21 is a block diagram of a body-implantable active device, in accordance with some embodiments of the invention:

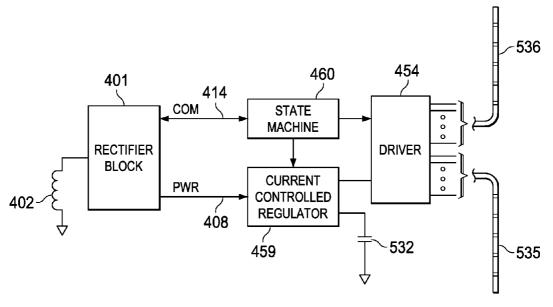

FIG. 22A illustrates a simplified block diagram of the IPG:

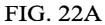

FIG. 22B illustrates a flow chart for the operation of the initiation of a neurostimulation program at the IPG;

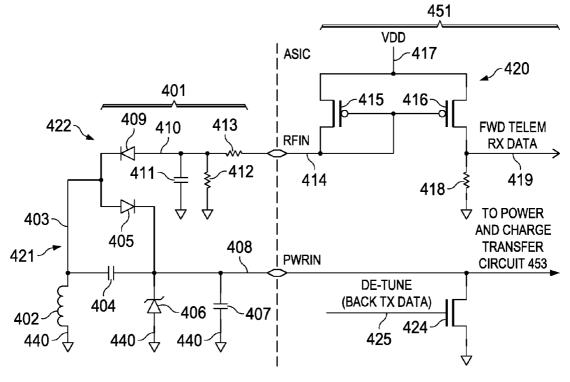

FIG. 23A is a schematic diagram of an exemplary rectifier FIG. 21. in accordance with some embodiments of the invention;

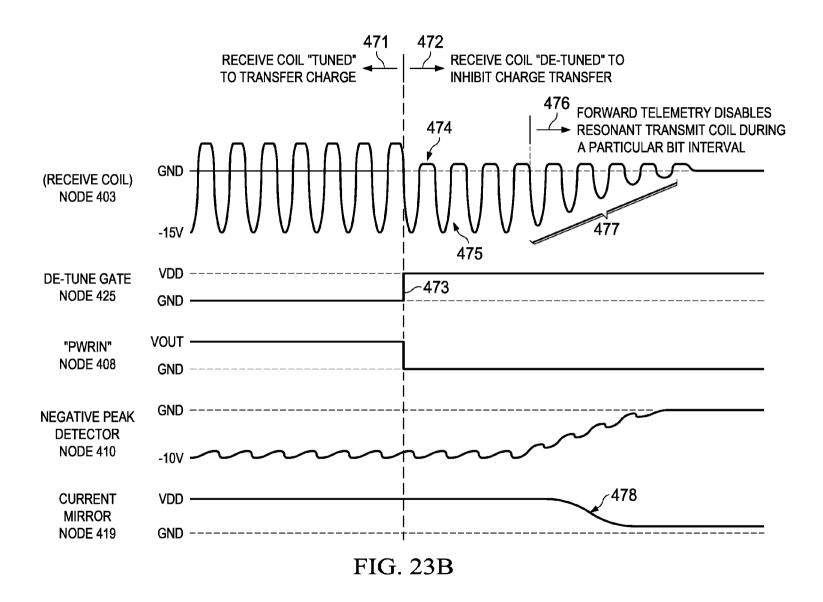

FIG. 23B illustrates voltage waveforms of selected signals depicted in the embodiment shown in FIG. 23A;

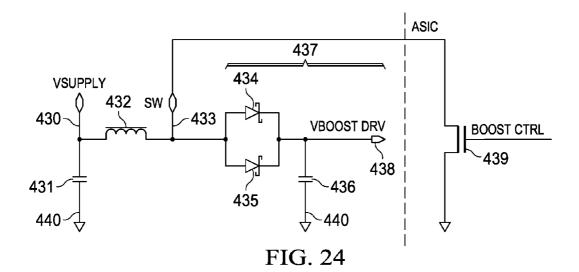

FIG. 24 is a schematic diagram of portions of an exemplary boost circuit, such as that shown in FIG. 21, in accordance with some embodiments of the invention;

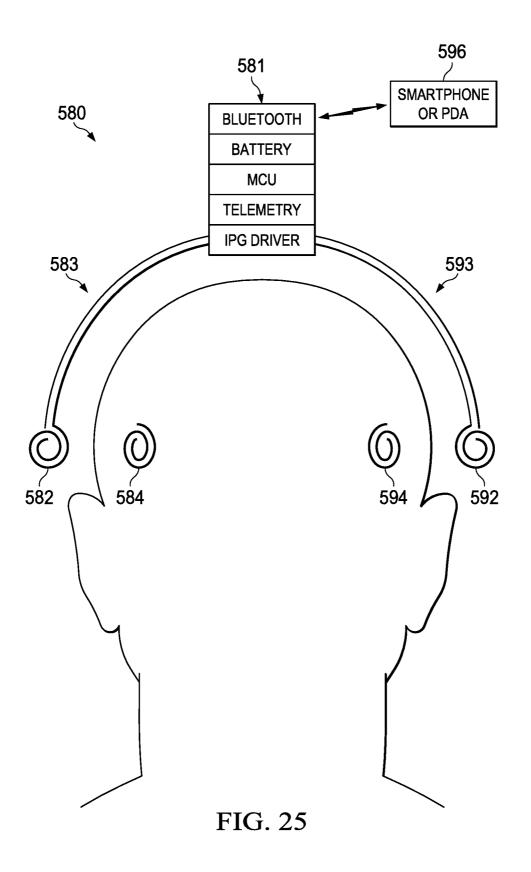

FIG. 25 is a diagram representing an exemplary headset that includes an external charge transfer system for two separate body-implantable devices, each implanted behind a patient's respective left and right ears, and shows an associated headset coil placed in proximity to the corresponding receive coil in each implanted device;

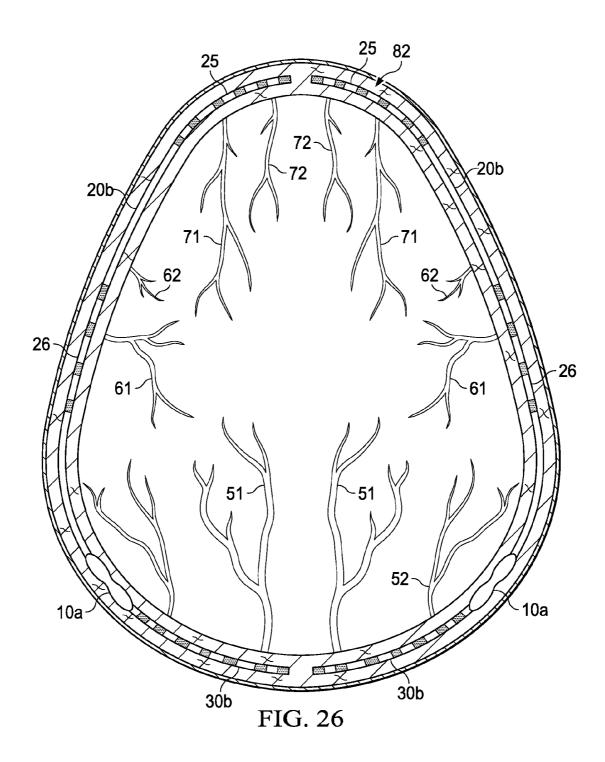

FIG. 26 depicts two implanted IPGs with leads to cover both sides of the head;

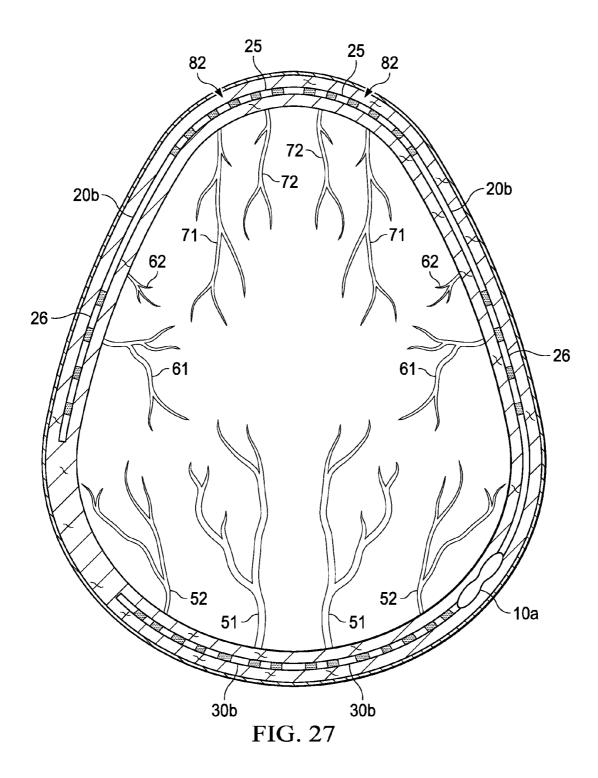

FIG. 27 depicts one implanted IPG with leads to cover both sides of the head;

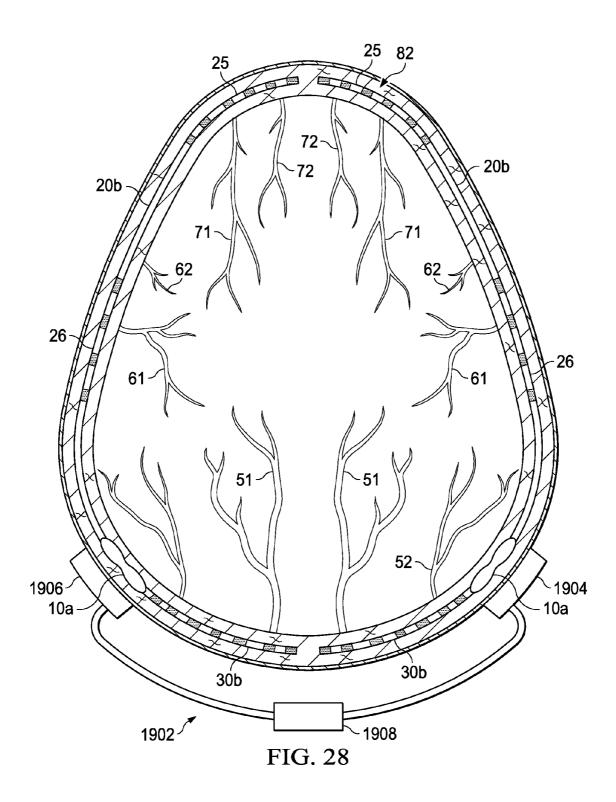

FIG. 28 illustrates the embodiment of FIG. 26 with a charging/communication headset disposed about the cranium;

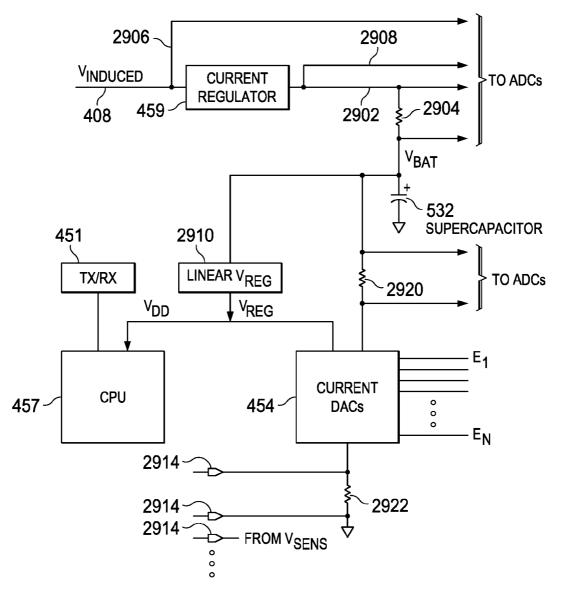

FIG. 29 illustrates a diagrammatic view of the power regulation system and current regulation system on the IPG;

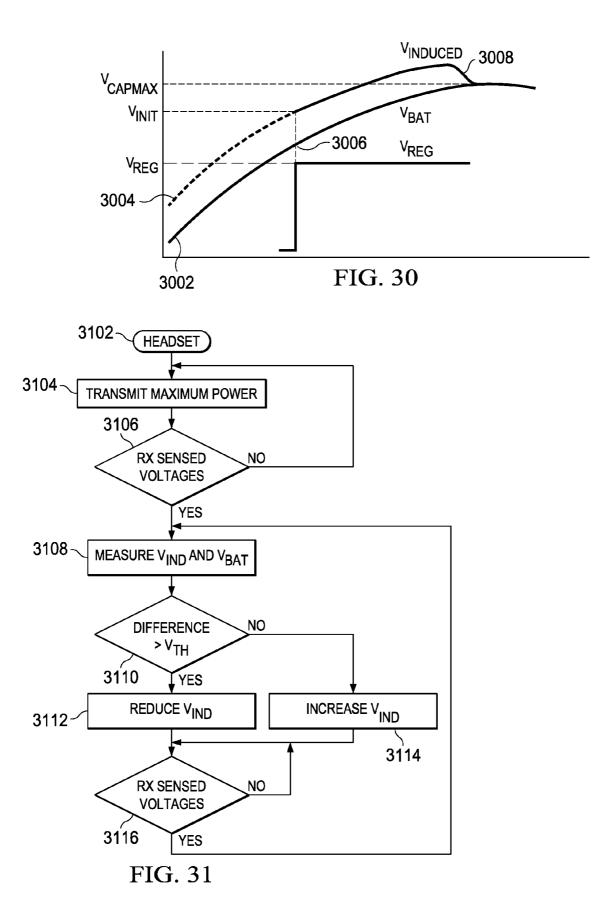

FIG. 30 illustrates a diagrammatic view of the voltage charging relationships for the supercapacitor; and

FIG. 31 illustrates a flowchart for power transfer system from the headset.

#### DETAILED DESCRIPTION

#### A. Introduction

Referring now to the drawings, wherein like reference numbers are used herein to designate like elements throughout, the various views and embodiments of an implantable 60 neurostimulation lead for head pain are illustrated and described, and other possible embodiments are described. The figures are not necessarily drawn to scale, and in some instances the drawings have been exaggerated and/or simplified in places for illustrative purposes only. One of ordinary skill in the art will appreciate the many possible applications and variations based on the following examples of possible embodiments.

The present disclosure provides for a fully head-located, radiofrequency-coupled, implantable peripheral neurostimulation system that is specifically designed for the treatment of chronic head pain. It incorporates multiple unique elements and features that take into account the 5 unique anatomic, physiologic, and other related challenges of treating head pain with implantable neurostimulation and, by doing so, greatly improves on therapeutic response, patient safety, medical risk, and medical costs, which combine to improve overall patient satisfaction.

Prior implantable peripheral neurostimulation systems and components, including leads and pulse generators, had been originally designed and developed specifically as spinal cord stimulator systems and for the specific therapeutic purpose of treating chronic back and extremity pain. Over 15 the years, however, these spinal cord stimulators were ultimately adopted and adapted for use as implantable peripheral nerve stimulators for the treatment of migraine headaches and other forms of chronic head pain. However, they were so utilized with full recognition of the inherent 20 risks and limitations due to the fact that they had been developed to only address, and accommodated to, the unique anatomic and physiologic features of the back and chronic back pain.

A number of problems have been recognized with respect 25 to spinal cord stimulators for head pain as fundamentally due to design flaws associated with, and inherent to, the use of an implantable therapeutic device in an area of the body that it was not designed for.

The anatomy of the head and the pathophysiology of 30 headaches and other forms of head pain are so significantly different from the anatomy of the spinal canal and pathophysiology of chronic back pain, that when spinal cord stimulators are utilized for cranial implants, the clinical problems associated with these differences manifest them- 35 selves. Importantly, these well-documented problems are clinically very significant and include issues of patient safety and satisfaction, the risk of an inadequate or suboptimal therapeutic response, issues with patient comfort and cosmetics, and a recognized increased risk of surgical compli- 40 cations and technical problems.

Prior implantable peripheral neurostimulation leads have been designed and developed specifically for placement in the spinal canal as part of a spinal cord stimulation system and for the specific therapeutic purpose of treating various 45 forms of chronic back and extremity pain. The present disclosure provides an implantable peripheral neurostimulation lead that is designed for the implantation in the head for the treatment of chronic head pain. It incorporates multiple unique elements and features that take into account 50 the unique anatomic, physiologic, and other related challenges of treating head pain with implantable neurostimulation and by doing so greatly improves on therapeutic response, patient safety, medical risk, medical costs, which combine to improve overall patient satisfaction.

Indeed, the anatomy of the head, and the pathophysiology of headaches and other forms of head pain that are unique to the head, are so significantly different from the anatomy of the spinal canal, and pathophysiology of chronic back pain that when these current leads are indeed utilized as cranial 60 implants, then the clinical problems associated with these differences manifest themselves. Specifically, these include issues with inadequate therapeutic responses, issues with patient comfort and cosmetics, and also very significant issues with patient safety.

These medical risks stem from the design of conventional leads and the IPG. Conventional lead designs include a

12

relatively large diameter, a cylindrical shape, (often) inadequate length, and the necessity of implanting the IPG in the torso and distant from the distal leads, and a number and disposition of the surface electrodes and active lead arrays that do not match the requirements. A cylindrical lead of relatively large diameter results in increased pressure on, and manifest tenting of, the overlying skin, particularly of the forehead. Because conventional leads are of inadequate length to extend from the head to the IPG implant site, commonly in the lower back, abdomen, or gluteal region, lead extensions are often employed, and there are attendant risks of infection, local discomfort, and cosmetic concerns.

With respect to prior leads: 1) There is only a single array of electrodes, with common lead options including 4, 8, or 16 electrodes disposed over that single array; 2) The array is relatively short with most leads having an array of from 5-12 cm in length; 3) Within this single array, the individual electrodes are disposed uniformly with constant, equal interelectrode distances. This results in the need to implant multiple (often four or more) of the conventional leads to adequately cover the painful regions of the head.

There are several practical clinical outcomes that result from the use of prior leads for the treatment of chronic head pain. First, since they comprise a single, relatively short active array, the currently available leads provide therapeutic stimulation to only a single region of the head; that is, they can provide stimulation to only the frontal region, or a portion of the parietal region, or a portion of the occipital region. Therefore, if a patient has pain that extends over multiple regions, then multiple separate lead implants are required—basically one lead implant is required for each unilateral region. A great majority of patients with chronic headaches experience holocephalic pain; that is they experience pain over the frontal and parietal and occipital regions bilaterally. Therefore, commonly these patients will need 4 to 7 leads implanted to achieve adequate therapeutic results (2 or 3 leads on each side).

Second, the need for multiple leads includes considerable added expense, and more importantly, added medical risk associated with adverse events attendant to the multiple surgical procedures. Such adverse events include an increased risk of infection, bleeding, and technical issues with the leads, e.g., lead fracture, lead migration, and local irritation.

Third, as the clinical database discloses, the inter-electrode spacing may be of central therapeutic significance. That is, for example, whereas commonly pain over the occipital region is consistently effectively treated by quadripolar leads (leads with four evenly spaced electrodes) that have the electrodes relatively widely spaced apart (approximately a cm or more apart), clinically it is often found that electrodes configurations that are more narrowly spaced may be more effective over the supraorbital nerve and regions. Thus, a quadripolar lead that has the electrodes only 1-2 mm 55 apart may be more effective in this region, as it allows for more precise control of the delivered electrical pulse wave delivery.

When an IPG implant for spinal cord stimulation systems is employed as a peripheral nerve stimulator for head pain, several outcomes result. First, the IPG is implanted at a considerable anatomic distance from the cranial lead implants. Indeed, the leads must pass from their distal cranial implant positions across the cervical region and upper back to the IPG implant location, which are most commonly in the lower back, lower abdomen, or gluteal region. The leads must cross multiple anatomic motion segments, including the neck and upper back and/or chest at

a minimum, and commonly include the mid back, lower back and waist segments, as well. The simple motions of normal daily life produce adverse tension and torque forces on the leads across these motion segments, which in turn increases the risk of various outcomes including lead migra-5 tion and/or lead fracture. In addition, the relatively large size of a spinal cord stimulator IPG contributes to local discomfort, cosmetic concerns, and increased risk of infection that may become larger and harder to treat in proportion to the size of the IPG pocket.

The present disclosure is directed to an implantable neurostimulation system that includes an IPG from which two neurostimulating leads extend to a length sufficient to allow for therapeutic neurostimulation unilaterally over the frontal, parietal and occipital regions of the head.

The present disclosure addresses and effectively solves problems attendant to publically available leads. The most important of these is the fact that currently available leads can only adequately stimulate a single region of the head due to design element flaws associated with terminal surface 20 electrode number and disposition. The disclosure additionally addresses and solves other problems inherent with the currently available leads, including problems with cosmetics and patient comfort, particularly over the frontal regions, due the uncomfortable pressure placed on the skin of the 25 forehead, due the cylindrical shape and relatively large diameter of the distal portion of the lead. Finally, the lead of the present disclosure solves the currently available leads' problem of inadequate lead length to reach a gluteal location of the implantable pulse generator, which therefore neces- 30 sitates the additional risk and expense of further surgery to implant lead extensions.

In one aspect, the implantable, head-mounted, neurostimulation system for head pain is operable for subcutaneous implantation in the head, and to provide neurostimula- 35 tion therapy for chronic head pain, including chronic head pain caused by migraine and other headaches, as well as chronic head pain due other etiologies. The peripheral neurostimulator system disclosed herein takes into account unique anatomic features of the human head, as well as the 40 unique, or singular, features of the various pathologies that give rise to head pain, including migraine and other headaches, as well as other forms of chronic head pain. To date, all commercially available leads and systems that have been clinically utilized for implantation as a peripheral neuro- 45 stimulator lead were actually originally designed specifically for placement in the epidural space, as part of a spinal cord stimulation system, for the therapeutic purpose of treating chronic back and/or extremity pain. Thus, there are currently no commercially available leads or full system that 50 have designs in the public domain, that have been designed and developed for use in the head and for head pain.

In another aspect, the implantable, head-mounted, neurostimulation system for head pain comprises multiple design features, including disposition of a sufficient plurality of 55 surface electrodes over a sufficient linear distance along the distal lead, such as will result in a lead that, as a single lead, is capable of providing medically adequate therapeutic stimulation over the entire hemicranium; that is, over the frontal, parietal, and occipital region stimulation. Currently 60 available systems, which were designed specifically for epidural placement for chronic back pain, are capable of only providing stimulation over a single region; that is, over either the frontal region alone, or the parietal region alone, or the occipital region alone. 65

In yet another aspect, the implantable peripheral neurostimulation system for head pain comprises multiple design features, including the physical grouping of the extended array of surface electrodes into three or more discrete terminal surface electrode arrays. The linear layout of these two or more (preferrably three or more) surface electrodes arrays is designed such that following implantation there would be at least one array positioned over the frontal region, at least one array positioned over the parietal region, and at least one array positioned over the occipital region. This feature further improves upon therapeutic effectiveness of the extended terminal surface electrode array sufficient for hemicranial stimulation by allowing for more precise control of the therapeutic neurostimulation parameters.

In still another aspect, the implantable, head-mounted, neurostimulation system for head pain comprises multiple design features, including incorporating individual design features within each of the three or more individual surface electrode arrays. Examples of such intra-array design features would include the specific number of electrodes allotted to each group; whether the electrodes are cylindrical or flattened: the width of each electrode within each array, and the linear distance intervals of separation of the electrodes within each array. This feature further improves upon therapeutic effectiveness of the extended terminal surface electrode array sufficient for hemicranial stimulation, and the grouping of these electrodes into three or more separate surface electrode arrays, by providing each specific array location a unique intra-array design that takes into account, and thereby seeks to optimizes, design elements that are known to be possibly or likely beneficial to the therapeutic end result, given the anticipated post-implant anatomic location of that array.

In yet another aspect, an implantable peripheral neurostimulation system for head pain comprises multiple novel design features, including incorporating individual design features into a single lead design and thereby achieving additive benefits.

In still another aspect, an implantable peripheral neurostimulation system for head pain results in a marked decrease in the number of separate lead implants required to adequately treat a single patient. A single implant will provide the same therapeutic anatomic coverage that it would take for the implantation of three or four of the currently available leads. That is, instead of the current which often calls for three or more leads to be implanted to provide adequate hemicranial coverage, the same anatomic region may be covered with a single stimulator lead implant. The lead provides extended coverage over the full hemicranium; that is, achieving medically acceptable neurostimulation unilaterally over the frontal, parietal, and occipital regions simultaneously. In contrast, publically known leads are able to consistently provide medically acceptable neurostimulation therapy only over a single region, meaning that it would require three separate surgically lead implants to achieve the same therapeutic coverage of a single implant of a lead of the present disclosure. This will decrease the total number of surgeries required, as well as the extent of each individual surgery for many patients.

In another aspect, by having a system that is fully localized to the head, it eliminates the requirement of currently available systems of having long leads and extensions extending across the neck and back to IPG locations commonly in the low back and gluteal region, and thereby decreases the risk of problems attendant to such long leads and extensions, including discomfort, infection, technical extension issues such as fracture, and other morbidities. This results in a further decrease in the number of surgeries required by a patient.

In other aspects, an IPG may be of proper aspect ratio with respect to the specific site of intended implantation in the head, preferably an area posterior to and/or superior to the ear. There may be an external portable programming unit that is capable of achieving a radiofrequency coupling to the 5 implanted unit. An IPG may have an internal RF receiver coil that is capable of coupling via a radiofrequency mechanism to an external control unit that provides power and control function. An IPG may contain an internal RF receiver, an application specific integrated circuit, and a 10 supercapacitor. In the event the external power supply is lost, the supercapacitor can supply power to the device and keep the device functioning until the external power connection can be resumed. The system may include a primary cell as a power source. An IPG may be capable of being 15 multiplexed, i.e., the IPG can be programmed to only stimulate (turn on) the required and necessary electrical contacts needed for therapy and turn off the ones not needed.

In other aspects, the system may include one or more of the following features. A neurostimulating lead may not 20 require a central channel for a stylet. A neurostimulating lead may have a smaller diameter than currently available leads. A neurostimulating lead may have a shaped or flat electrode design that orients the electrical fields toward the specific nerves, thus avoiding stimulation of undesired tissues, e.g., 25 adjacent muscles, while additionally improving patient cosmetics. A neurostimulating lead may include redundant electrodes for the shaped or flat electrode contacts such that in the event the leads are inadvertently flipped, these redundant electrodes can be selected and activated so that the 30 electric fields can still be oriented at the proper nerves.

In other aspects, the system may include one or more of the following features. The system may include the disposition of a sufficient plurality of surface electrodes over a sufficient linear distance along the system's leads to enable 35 medically adequate therapeutic stimulation across multiple regions of the head, and preferably the entire hemicranium; that is, over the frontal, parietal, and occipital region simultaneously. The extended array of surface electrodes may be divided into two or more discrete terminal surface electrode 40 arrays. The preferred linear layout of these multiple surface electrode arrays includes at least one array positioned over the frontal region, at least one array positioned over the parietal region, and at least one array positioned over the occipital region.

In other aspects, intra-array design features may include variations in the specific number of electrodes allotted to each group; the shape of the electrodes, e.g., whether the electrodes are cylindrical or flattened; the width of each electrode within each array, and the linear distance intervals 50 of separation of the electrodes within each array.

In other aspects, the system may include a plurality of connection ports that can be connected with a plurality of leads and thus allow for attaching additional leads should they later be required.

In another aspect, an implantable peripheral neurostimulation system for head pain comprises multiple design features; including features aimed at improving patient safety by improving the incidence of adverse events, including the risk of infection, as well as the risk and incidence of 60 known technical problems associated with implanted leads, including lead migration and lead fracture, amongst others. The lead may comprise two or more (i.e. three or more) surface electrode arrays, each uniquely designed, that are disposed over a sufficient lead length to allow for medically 65 acceptable therapeutic neurostimulator coverage of at least regions within the supraorbital, parietal, and occipital cranial

regions. To achieve the same clinical coverage from a single implant, it would require three or more separately surgically implanted leads. Therefore, by reducing the number of surgical incisions, as well as the number of surgically implanted leads, the associated risks of adverse events are proportionally diminished.

In yet another aspect, an implantable peripheral neurostimulation system for head pain may treat chronic head and/or face pain of multiple etiologies, including migraine headaches; and other primary headaches, including cluster headaches, hemicrania continua headaches, tension type headaches, chronic daily headaches, transformed migraine headaches; further including secondary headaches, such as cervicogenic headaches and other secondary musculoskeletal headaches; including neuropathic head and/or face pain, nociceptive head and/or face pain, and/or sympathetic related head and/or face pain; including greater occipital neuralgia, as well as the other various occipital neuralgias, supraorbital neuralgia, auroiculotemporal neuralgia, infraorbital neuralgia, and other trigeminal neuralgias, and other head and face neuralgias.

In another aspect, an implantable, head-mounted, neurostimulation system for head pain comprises multiple design features, including features aimed at improving patient safety by improving the incidence of adverse events, including the risk of infection, as well as the risk and incidence of known technical problems associated with implanted leads, including lead migration and lead fracture, amongst others. The lead may comprise two or more (i.e. three or more) surface electrode arrays, each uniquely designed, that are disposed over a sufficient lead length to allow for medically acceptable therapeutic neurostimulator coverage of at least regions within the supraorbital, parietal, and occipital cranial regions. To achieve the same clinical coverage from a single implant, it would require three or more separately surgically implanted leads. Therefore, by reducing the number of surgical incisions, as well as the number of surgically implanted leads, the associated risks of adverse events are proportionally diminished.

In yet another aspect, an implantable, head-mounted, neurostimulation system for head pain may treat chronic head and/or face pain of multiple etiologies, including migraine headaches and other primary headaches, including cluster headaches, hemicrania continua headaches, including cluster headaches, hemicrania continua headaches, tension type headaches, chronic daily headaches, transformed migraine headaches, further including secondary headaches, such as cervicogenic headaches and other secondary musculoskeletal headaches, including neuropathic head and/or face pain, nociceptive head and/or face pain, and/or sympathetic related head and/or face pain, including greater occipital neuralgia, as well as the other various occipital neuralgias, supraorbital neuralgia, auroiculotemporal neuralgia, infraorbital neuralgia, and other trigeminal neuralgias, and other head and face neuralgias.

In other aspects, an implantable, head-mounted, neurostimulation system for head pain may not require a central channel for stylet placement over its distal (frontal) portions. The lead may improve patient comfort and cosmetics by virtue of its relatively small diameter over the distal portions of the lead, partially due the lack of a central stylet channel, as well as due to a progressive decrease in the number of internal wires continuing after each terminal electrode. The lead may further improve cosmetic appearance and patient comfort by incorporating a flattened lead design for that portion of the lead expected to be over the frontal portion of the head.

35

Thus, the present disclosure provides for a peripheral neurostimulation lead that is uniquely designed for implantation in the head as a therapy for chronic head pain, and is designed to solve the known design issues associated with current leads, as the lead of the present disclosure seeks to optimize the therapeutic response, improve patient comfort, improve cosmetics, reduce the number of surgical leads required, and reduce medical risk, and reduce medical costs.

#### B. Overview

Turning now descriptively to the drawings, in which similar reference characters denote similar elements throughout the several views, the figures illustrate an implantable pulse generator (IPG) from which two neurostimulating leads may extend to a length sufficient to allow for therapeutic neurostimulation unilaterally over the frontal, parietal and occipital regions. The leads include an extended plastic lead body, a plurality of surface metal 20 electrodes disposed along the lead, which may be divided into two or more electrode arrays, a plurality of internal electrically conducting metal wires running along at least a portion of its length and individually connecting the IPG's internal circuit to individual surface metal electrodes. The 25 implantable pulse generator includes the internal circuits, a radiofrequency receiver coil, and an ASIC. The system may be operable to provide medically acceptable therapeutic neurostimulation to multiple regions of the head, including the frontal, parietal and occipital regions simulataneously, 30 and six figures demonstrate various views of this feature as the system is depicted in situ.

# C. Full Head-Located Neurostimulator System

FIG. 1 depicts a side view of a full neurostimulator system, which consists of an implantable pulse generator (IPG) 10 along with two unibody plastic lead extensions—a Fronto-Parietal Lead (FPL) 20 and an Occipital Lead (OL) 30 of adequate length to extend to roughly the midline of the forehead and to the midline at the cervico-cranial junction, respectively. Arrows 28 indicate the point of cross section of FIG. 4.

FIGS. **5**, **6**, and **7** depict posterior, lateral and frontal 45 views of the system in-situ. The unit is demonstrated in an implant position where the IPG **10** is posterior and cephalad to the pinna of the ear. The drawings demonstrate the FPL **20** passing over the parietal **60** and frontal **70** regions of the head, including auriculo-temporal nerve **61** and supraorbital 50 nerve **71**, in a manner that places the FEA over the supraorbital nerve and the PEA over the auriculotemporal nerve. The OL **30** is shown passing caudally and medially over the occipital region of the head such that the OEA **35** cross over the greater occipital nerve **51**, the lesser occipital nerve **52**, 55 and the third occipital nerve.

FIGS. 8 and 9 depict two views of the external control unit (ECU) 100. FIG. 8 depicts a side view of an ECU 100, the components of which include an ear clip 1110, an electronics and battery component (EBC) 1120, an external coil lead 60 1130, and an external RF coil housing 1140 that contains a RF coil 1141 external magnet 1142. FIG. 9 depicts a right oblique frontal view of the head with an implantable neurostimulator system in-situ, and with the ECU 100 attached to the ear in its functional position, with the external RF coil 11 and internal magnet 12 of the IPG 10.

### D. Fronto-Parietal Lead

Continuing with FIG. 1, the FPL 20, as part of the unibody construction, extends from the IPG. The FPL comprises a plastic body member 20a and a set of internal conducting wires 29.

The plastic body member 20*a* is an elongated, cylindrical, flexible member, which may be formed of a medical grade plastic polymer. It has a proximal end 22, a distal end 21, and may be conceptually divided into five segments along its linear dimension. Progressing from the proximal end 22, these segments sequentially include a proximal lead segment (PLS) 22*a*, a parietal electrode array (PEA) 26, an interarray interval 27, a frontal electrode array (FEA) 25, and a distal non-stimulating tip 23.

The lead internal wires **29** pass along the interior of the plastic body member as depicted in FIG. **4**.

#### E. Frontal Electrode Array

Continuing with FIG. 1, the FEA 25 consists of a plurality of surface metal electrodes (SME) 24 uniformly disposed over a portion of the distal aspect of the FPL 20. Lead internal wires 29 connect to the SME 24 as depicted in FIG. 2, which represents the distal four SME 24 of the lead.

### F. Parietal Electrode Array

Returning to FIG. 1, the PEA 26 consists of a plurality of SME 24 uniformly disposed along a linear portion of the FPL. The PEA 26 is separated along the FPL from the FEA by an inter-array interval 27. It is separated only the lead from the IPG by the PLS 22*a*. The lead internal wires 29 connect to the individual SMEs 24 of the PEA in the same fashion as the do with the SME of the FEA as shown in FIG. 2.

# G. Occipital Lead

Continuing with FIG. 1, the occipital lead (OL) **30** as part of the unibody construction extends from the IPG **10**. It comprises a plastic body member **39** and a set of lead internal wires **38** that pass through the central cylinder of the lead to connect to a series of SME **34**, each of surface electrode width **37**, that are uniformly disposed at an interelectrode distance **36** from each other along a portion of the length of the lead. These lead internal wires **38** pass and connect in the same manner as described above for the SME **24** of the FEA **25** as depicted in FIGS. **2** and **4**.

The plastic body member **39** is an elongated, cylindrical, flexible member, which may be formed of a medical grade plastic polymer. It has a proximal end **32** and a distal end **31**. Progressing along the lead from the proximal end **32**, these segments sequentially include a proximal lead segment (PLS) **32***a*, an occipital electrode array (OEA) **35**, and a distal non-stimulating tip **23**.

# H. Occipital Lead Array

As depicted in FIG. 1, the OEA 35 consists of a plurality of surface metal electrodes (SME) 34 uniformly disposed over a portion OL 30. Lead internal wires 38 connect to the SME 24 in the same fashion as depicted for the FEA 25 as shown in FIG. 2.

#### I. Implantable Pulse Generator

Referring to FIG. 1 and FIG. 3, the three primary physical and functional components of the IPG 10 include an internal

60

magnet 12, an internal radiofrequency receiver coil 11, and an application specific integrated circuit (ASIC) 13, along with the necessary internal wire connections amongst these related components, as well as to the incoming lead internal wires **29**, **39**. These individual components may be encased 5 in a can made of a medical grade metal and plastic cover 14. which itself transitions over the exiting FPL 20 and OL 30.